# 5 FC-1 transmission codes

# 5.1 Overview

Transmission codes are a function of the FC-1 level. Communication of words and Special Functions are FC-1 functions. Use of Special Functions is an FC-2P function.

Information to be transmitted over a fibre shall be presented to the FC-1 level as a stream of words and Special Functions. It shall be encoded using one of the transmission codes specified in this clause into a stream of Transmission Words that shall be sent across the link. Information shall be received over the link as a stream of Transmission Words. The stream of Transmission Words shall be decoded using one of the transmission codes specified in this clause into a stream of words and Special Functions that shall be decoded using one of the transmission codes specified in this clause into a stream of words and Special Functions that shall be delivered to the FC-2P sublevel.

This standard specifies two types of transmission codes:

- a) frame transfer transmission codes are specified to transfer Upper Level Protocol data; and

- b) other transmission codes (e.g., the Transmitter Training Signal, see 5.6) are specified for purposes other than transferring Fibre Channel frames.

Both types of transmission code provide these functions:

- a) maintaining Bit Synchronization and Transmission Word Synchronization;

- b) communicating link control information; and

- c) increasing the likelihood of detection of transmission errors.

Frame transfer transmission codes additionally provide these functions:

- a) communicating link state machine transitions;

- b) communicating other Special Functions;

- c) denoting frame boundaries; and

- d) communicating Upper Level Protocol data.

The encodings defined by the transmission code ensure that sufficient transitions are present in the serial bit stream to make clock recovery possible at the receiver. Such encoding also increases the likelihood of detecting any single or multiple bit errors that may occur during transmission and reception of information. In addition, the transmission code assures presence of a distinct and easily recognizable bit pattern that assists a receiver in achieving Transmission Word alignment on the incoming bit stream.

An FC-0 standard for a physical variant may specify a transmission code. If an FC-0 standard for a physical variant does not specify a transmission code, then the physical variant shall use the 8B/10B transmission code (see ).

# 5.4 32GFC 256B/257B transmission code

### 5.4.1 Overview

An FC-0 standard (e.g., FC-PI-6) may specify the use of the <u>32GFC</u> 256B/257B transmission code as its frame transfer transmission code. If the <u>32GFC</u> 256B/257B transmission code is specified, then it shall be:

- a) generated as described in 5.4.2;

- b) encoded with Reed Solomon coding as described in 5.4.3;

- c) scrambled as described in 5.4.4;

- d) descrambled as described in 5.4.5;

- e) decode with the Reed Solomon decoder as described in 5.4.6; and

- f) decoded as described in 5.4.7.

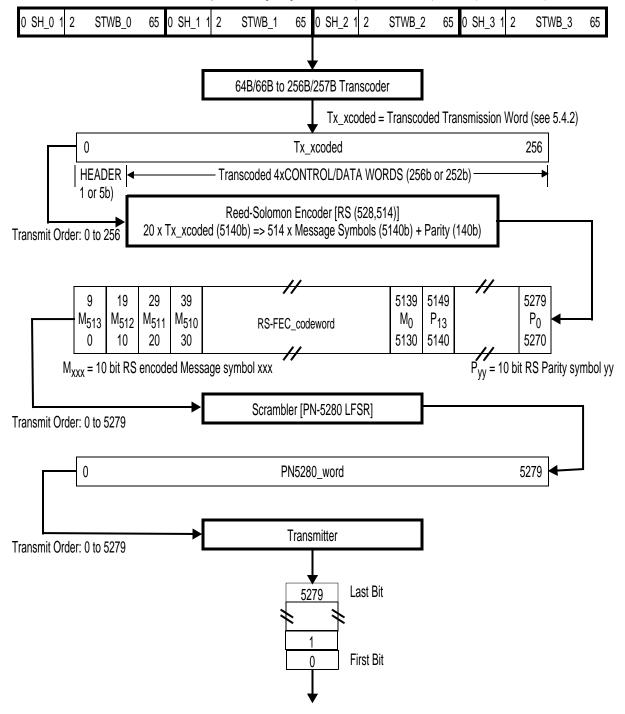

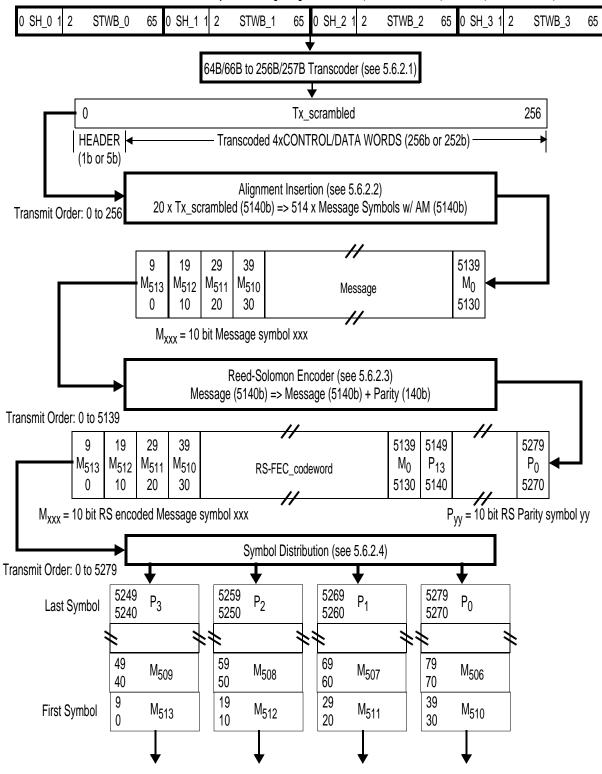

# 5.4.2 64B/66B to 256B/257B Transcoding

The 256B/257B transmission code specified by this standard operates on 4 consecutive 64B/66B Transmission Words (see 5.3), each group being encoded as a 257-bit Transmission Word.

NOTE 1 - The IEEE 802.3bj-2014 specification of 256B/257B references as "blocks" what this standard references as "Transmission Words".

The transcoder constructs a 257-bit Transmission Word from a group of 4 x 66-bit Transmission Words to allocate bandwidth for the parity check symbols added by the Reed-Solomon encoder.

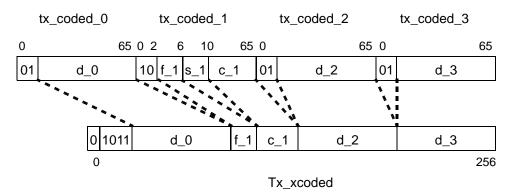

The 257-bit Transmission Word tx\_xcoded<256:0> shall be constructed as defined in IEEE 802.3bj-201X 91.5.2.5 given 4 x 66-bit Transmission Words denoted as tx\_coded\_j<65:0> where j=0 to 3. The first 5 bits of tx\_xcoded<256:0> are not scrambled (i.e., the step that generates tx\_scrambled<256:0> is not performed).

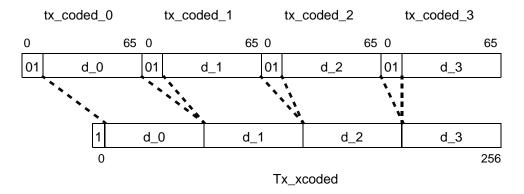

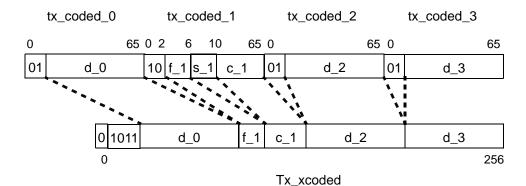

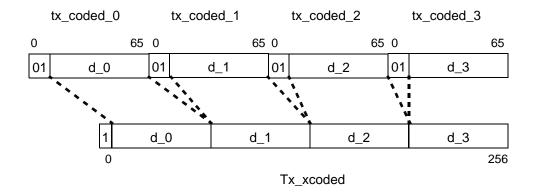

Figure 10 shows the 32GFC 256B/257B encoding of four data words.

Key: \_x = data from the encoded 64/66b block

Figure 10 - 32GFC 256B/257B encoding of four data words

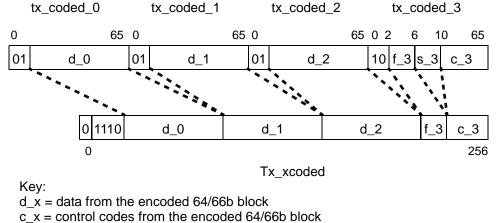

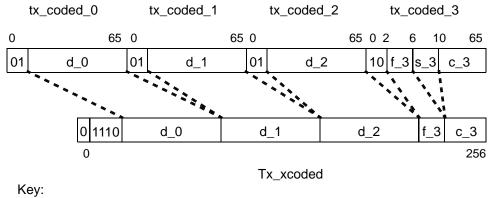

Figure 11 shows the <u>32GFC</u> 256B/257B encoding of three data words followed by one control word.

$f_x =$ first 4 bits of the block type field in he encoded 64/66b block

$s_x =$  second4 bits of the block type field in the encoded 64/66b block

#### Figure 11 - 32GFC 256B/257B encoding of three data words followed by one control word

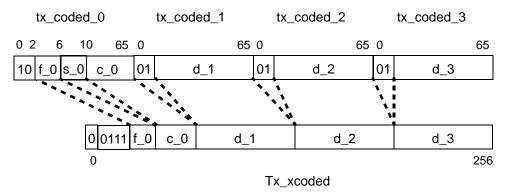

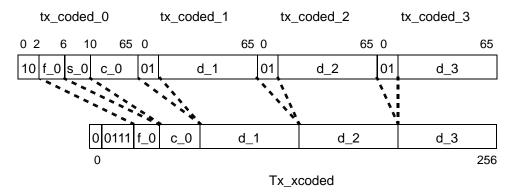

Figure 12 shows the 32GFC 256B/257B encoding of one control word followed by three data words.

Key:

d  $\dot{x}$  = data from the encoded 64/66b block

$c_x = control codes from the encoded 64/66b block$

$f_x =$ first 4 bits of the block type field in the encoded 64/66b block

$s_x = second 4$  bits of the block type field in the encoded 64/66b block

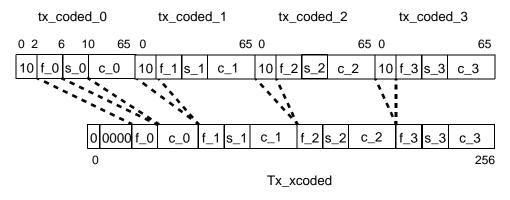

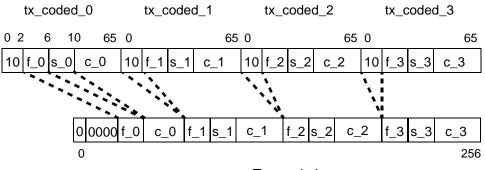

Figure 13 shows the 32GFC 256B/257B encoding of four control words.

Key:

$d_x = data$  from the encoded 64/66b block

$c_x = control codes$  from the encoded 64/66b block

$f_x =$ first 4 bits of the block type field in the encoded 64/66b block

$s_x =$  second 4 bits of the block type field in the encoded 64/66b block

#### Figure 13 - 32GFC 256B/257B encoding of four control words

Figure 14 shows the <u>32GFC</u> 256B/257B encoding of one data word followed by one control word followed by two data words.

Key:

d  $\dot{x}$  = data from the encoded 64/66b block

c x =control codes from the encoded 64/66b block

$f_x =$ first 4 bits of the block type field in the encoded 64/66b block

s x = second 4 bits of the block type field in the encoded 64/66b block

# Figure 14 - 32GFC 256B/257B encoding of one data word, followed by one control word, followed by two data words

A stream of 32GFC 256B/257B Transmission Words on a link shall be further encoded to provide Forward Error Correction (i.e., FEC).

The streams of 32GFC 256B/257B Transmission Words in both directions on the link shall be encoded as specified in 5.4 and then further encoded as specified in subclause 91.5.2.7 of IEEE 802.3bj-2014.

### 5.4.3 Reed-Solomon encoder

The RS-FEC sublayer employs a Reed-Solomon code (see bibliography Annex M) operating over the Galois Field  $GF(2^{10})$  (see bibliography Annex M) where the symbol size is 10 bits. The encoder processes k message symbols to generate 2t parity symbols which are then appended to the message to produce a code word of n=k+2t symbols. For the purposes of this clause, a particular Reed-Solomon code is denoted RS(n, k).

The RS-FEC sublayer shall implement RS(528, 514). Each k-symbol message corresponds to twenty 257-bit Transmission Words produced by the transcoder. Each code is based on the generating polynomial given by Equation 91–1 of IEEE 802.3bj-2014.

### 5.4.4 Scrambler

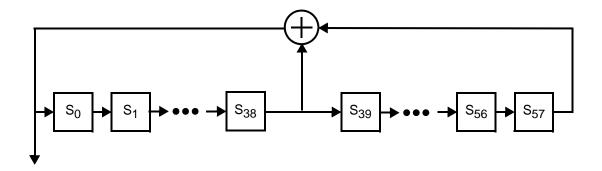

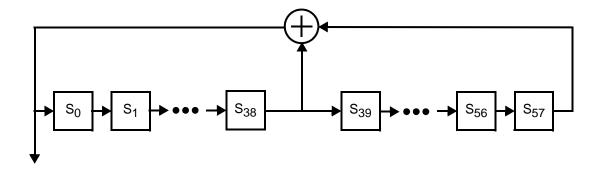

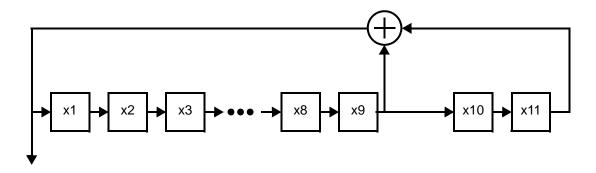

Each RS-FEC code word is scrambled with a known sequence to randomize the 257-bit Transmission Word headers and to enable robust code word synchronization at the receiver (i.e., ensure that any shifted input bit sequence is not equal to another RS-FEC code word). Scrambling is implemented as modulo 2 addition of the RS-FEC code word and a pseudo-noise sequence 5280 bits in length defined as PN-5280 (see figure 15).

PN-5280 is generated by the polynomial r(x).

$r(x) = x^{39} + x^{58} + 1$

Figure 15 - PN-5280 as a linear feedback shift register

At the start of each RS-FEC code word, the initial state of the pseudo-noise generator is set to:

$S_{57} = 1$

$S_{i-1} = S_i XOR 1$

(i.e., a binary sequence of alternating 1's and 0's).

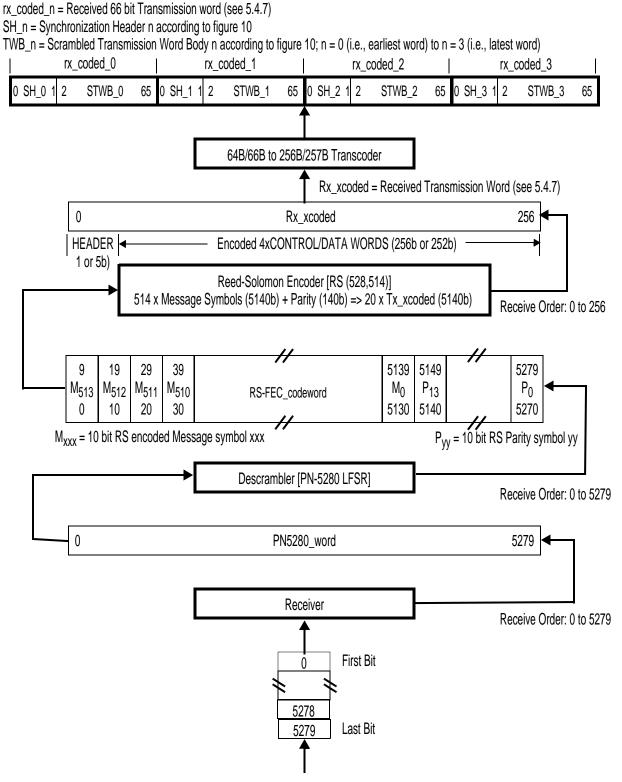

### 5.4.5 Descrambler

Each code word shall be descrambled prior to decoding. Descrambling is implemented as the modulo 2 addition of RS-FEC code word and the same pseudo-noise sequence PN-5280 defined for the scrambler (see 5.4.4).

### 5.4.6 Reed-Solomon decoder

The Reed-Solomon decoder extracts the message symbols from the code word, correcting them as necessary, and discards the parity symbols. The message symbols correspond to 20 x 257-bit Transmission Words.

The Reed-Solomon decoder shall be capable of correcting any combination of up to t=7 symbol errors in a code word. It shall also be capable of indicating when a code word contains errors but was not corrected (e.g., it contains a number of errors in excess of the error correction capability).

#### 5.4.7 32GFC 256B/257B to 64B/66B transcoder

The transcoder reconstructs a group of 4 x 66-bit Transmission Words from each received 257-bit Transmission Word.

The 4 x 66-bit Transmission Words, denoted as  $rx\_coded\_j<65:0>$  where j=0 to 3, shall be derived from each 257-bit Transmission Word  $rx\_xcoded<256:0>$  as defined in IEEE 802.3bj-2014 91.5.3.5. As the first 5 bits of  $rx\_xcoded<256:0>$  are not scrambled, the step defined in 802.3bj that derives  $rx\_xcoded$  from  $rx\_scrambled$  is not performed on those bits.

# 5.4.8 Transmit Bit Ordering

Transmit bit ordering for 32GFC 256B/257B is as shown in figure 16.

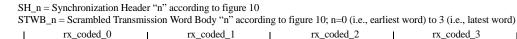

SH\_n = Synchronization Header n according to figure 10

TWB\_n = Scrambled Transmission Word Body n according to figure 10; n = 0 (i.e., earliest word) to n = 3 (i.e., latest word)

Figure 16 - 32GFC 256B/257B transmit bit ordering

# 5.4.9 Receive Bit Ordering

Receive bit ordering for 32GFC 256B/257B is as shown in figure 17.

Figure 17 - 32GFC 256B/257B receive bit ordering

# 5.5 64GFC 256B/257B transmission code

### 5.5.1 Overview

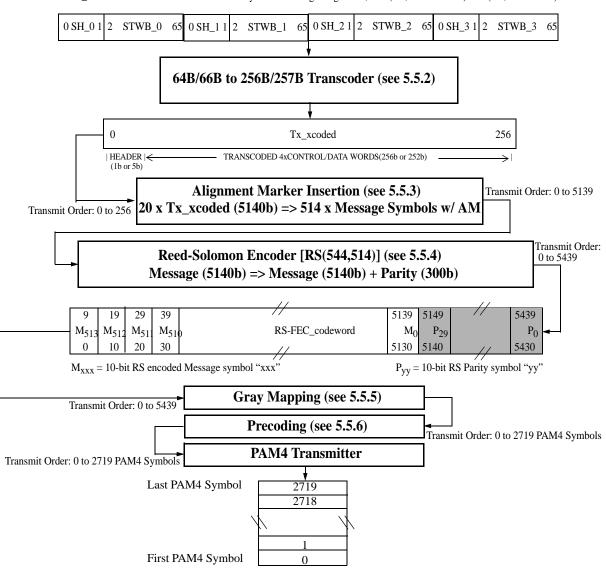

An FC-0 standard (e.g., FC-PI-7) may specify the use of the 64GFC 256B/257B transmission code as its frame transfer transmission code. If the 64GFC 256B/257B transmission code is specified, then it shall be:

- a) generated as described in 5.5.2 and 5.5.3;

- b) encoded with Reed Solomon coding as described in 5.5.4;

- c) Gray mapped scrambled as described in 5.5.5;

- d) when enabled, precoded as described in 5.5.6;

- e) when enabled, inverse precoded as described in 5.5.7;

- f) inverse Gray mapped descrambled as described in 5.5.8;

- g) decoded with the Reed Solomon decoder as described in 5.5.145.5.10; and

- h) <u>recovered</u> decoded as described in <u>5.4.7</u>5.5.11 and <u>5.5.12</u>.

### 5.5.2 64B/66B to 64GFC 256B/257B **T**ranscoding

64B/66B to 256B/257B transcoding is done as specified in 5.8.2.1.

The 64GFC 256B/257B transmission code specified by this standard operates on 4 consecutive 64B/66B Transmission Words (see 5.3), each group being encoded as a 257-bit Transmission Word.

NOTE 2 - The IEEE 802.3bj-2014 specification of 256B/257B references as "blocks" what this standard references as "Transmission Words".

The transcoder constructs a 257-bit Transmission Word from a group of 4 x 66-bit Transmission Words to allocate bandwidth for the parity check symbols added by the Reed-Solomon encoder.

The 257-bit Transmission Word tx\_xcoded<256:0> shall be constructed as defined in IEEE 802.3bj-201X 91.5.2.5 given 4 x 66-bit Transmission Words denoted as tx\_coded\_j<65:0> where j=0 to 3. The first 5 bits of tx\_xcoded<256:0> are not scrambled (i.e., the step that generates tx\_scrambled<256:0> is not performed).

#### Figure 10 shows the 64GFC 256B/257B encoding of four data words.

Key:  $_x = data from the encoded 64/66b block$

#### Figure 18 - 64GFC 256B/257B encoding of four data words

Figure 11 shows the 256B/257B encoding of three data words followed by one control word.

$d_x = data$  from the encoded 64/66b block

c\_x = control codes from the encoded 64/66b block

$f_x =$ first 4 bits of the block type field in he encoded 64/66b block

$s_x = second4$  bits of the block type field in the encoded 64/66b block

Figure 19 - 64GFC 256B/257B encoding of three data words followed by one control word

#### Figure 12 shows the 64GFC 256B/257B encoding of one control word followed by three data words.

Key:

$d_x = data$  from the encoded 64/66b block

c x =control codes from the encoded 64/66b block

f x = first 4 bits of the block type field in the encoded 64/66b block

$s_x =$  second 4 bits of the block type field in the encoded 64/66b block

#### Figure 20 - 64GFC 256B/257B encoding of one control word followed by three data words

Figure 13 shows the 64GFC 256B/257B encoding of four control words.

Tx\_xcoded

Key:

$d_x = data$  from the encoded 64/66b block

$c_x = control codes from the encoded 64/66b block$

$f_x =$ first 4 bits of the block type field in the encoded 64/66b block

$s_x =$  second 4 bits of the block type field in the encoded 64/66b block

Figure 21 - 64GFC 256B/257B encoding of four control words

#### T11-2017-00171-v002

Figure 14 shows the 64GFC 256B/257B encoding of one data word followed by one control word followed by two data words.

Key:

$d_x = data$  from the encoded 64/66b block  $c_x = control codes$  from the encoded 64/66b block

$f_x =$  first 4 bits of the block type field in the encoded 64/66b block

s x = second 4 bits of the block type field in the encoded 64/66b block

# Figure 22 - 64GFC 256B/257B encoding of one data word, followed by one control word, followed by two data words

A stream of 64GFC 256B/257B Transmission Words on a link shall be further encoded to provide Forward Error Correction (i.e., FEC).

The streams of 64GFC 256B/257B Transmission Words in both directions on the link shall be encoded as specified in 5.4 and then further encoded as specified in subclause 91.5.2.7 of IEEE 802.3bj 2014.

#### 5.5.3 Alignment marker mapping and insertion

The alignment insertion function inserts a unique data pattern (i.e., Alignment Marker) into the data stream to provide a framing pattern for aligning the FEC code words.

The first 257b of every 1024th FEC code word carries Alignment Marker information. The first 256 bits (0 to 255) of the Alignment Marker (AM) vector are composed of AMO, AM4, AM8 and AM12 from Table 82-2 of IEEE 802.3-2015. AMx is the marker for PCS lane number x in Table 82-2. AM0 is the first marker transmitted on the line, followed by AM4, AM8 and AM12. Each octet in the AM vector is transmitted LSB(rightmost bit) to MSB (leftmost bit) starting from the leftmost octet to the rightmost octet. The last bit (256) is a pad bit that is always transmitted as zero.

The BIP3 octet of AM0 carries Link degrade information associated with the link degrade function (see 5.5.10.1). The bits of this octet are assigned as follows:

BIP3[0]=RD, BIP3[3:1]=0 (Reserved for future use; Transmitted as zero) and BIP3[7:4]=0xA

The RD (Remote Degrade) indicator is in bit 24 of the AM[256:0] vector. The BIP7 octet is the bit-wise inverse of BIP3 but conveys no useful information. As an example, the first 32 bits of the AM vector are ordered as follows:

1000 0011 0001 0110 1000 0100 RD000 0101

For all other markers besides AM0, BIP3=0xAA and BIP7=0x55.

## 5.5.4 Reed-Solomon encoder

The RS-FEC sublayer employs a Reed-Solomon code (see bibliography Annex M) operating over the Galois Field  $GF(2^{10})$  (see bibliography Annex M) where the symbol size is 10 bits. The encoder processes k message symbols to generate 2t parity symbols which are then appended to the message to produce a code word of n=k+2t symbols. For the purposes of this clause, a particular Reed-Solomon code is denoted RS(n, k).

The RS-FEC sublayer shall implement RS(54428, 514) as defined in IEEE 802.3cd D2.2 <u>134.5.2.7</u>. Each k-symbol message corresponds to twenty 257-bit Transmission Words produced by the transcoder. Each code is based on the generating polynomial given by Equation 91–1 of IEEE 802.3-2015.

### 5.5.5 SeramblerGray mapping

The Gray mapping process shall map consecutive pairs of bits {A, B}, where A is the bit arriving first, to a Gray-coded symbol as follows:

{0, 0} maps to 0,

{0, 1} maps to 1,

{1, 1} maps to 2, and

{1, 0} maps to 3.

Each RS-FEC code word is scrambled with a known sequence to randomize the 257-bit Transmission Word headers and to enable robust code word synchronization at the receiver (i.e., ensure that any shifted input bit sequence is not equal to another RS-FEC code word). Scrambling is implemented as modulo 2 addition of the RS-FEC code word and a pseudo-noise sequence 5280 bits in length defined as PN-5280 (see figure 15).

PN-5280 is generated by the polynomial r(x).

$r(x) = x^{39} + x^{58} + 1$

Figure 23 - PN-5280 as a linear feedback shift register

At the start of each RS-FEC code word, the initial state of the pseudo-noise generator is set to:

- <del>S<sub>57</sub> = 1</del>

- S<sub>i\_1</sub> = S<sub>i</sub> XOR 1

(i.e., a binary sequence of alternating 1's and 0's).

# 5.5.6 Descrambler Precoding

The transmit process shall provide 1/(1+D) mod 4 precoding capability for electrical variants specified in FC-PI-7.

For each Gray-coded symbol G(*j*), a precoded symbol P(*j*) shall be determined by the following algorithm, where *j* is an index indicating the symbol number:

$P(j) = (G(j) - P(j-1)) \mod 4$

The decision to enable or disable transmitter precoding is determined by the remote receiver during the transmitter training process (refer to section 5.7 Transmitter Training Signal (TTS) for 64GFC Transmitter Training for details).

Each code word shall be descrambled prior to decoding. Descrambling is implemented as the modulo 2 addition of RS-FEC code word and the same pseudo-noise sequence PN-5280 defined for the scrambler (see 5.4.4).

# 5.5.7 Inverse precoding

The receive process optionally provides inverse precoding for electrical variants specified in FC-PI-7. When implemented and enabled, for each precoded symbol P(*j*), a Gray-code symbol G(*j*) shall be determined by the following algorithm:

$G(j) = (P(j) + P(j-1)) \mod 4$

When implemented, the decision to enable or disable remote transmitter precoding and receiver inverse precoding is determined by the receiver during the transmitter training process. The method by which the receiver determines whether or not to enable precoding is implementation dependent and beyond the scope of this standard.

# 5.5.8 Inverse Gray mapping

The inverse Gray mapping process shall map Gray-coded PAM4 symbols to pairs of bits {A, B} where A is considered to be the first bit as follows:

0 maps to {0, 0},

1 maps to {0, 1},

2 maps to {1, 1}, and

3 maps to {1, 0}.

### 5.5.9 Alignment lock

The receive function obtains LOCK to the alignment markers as specified by the FEC synchronization state diagram in IEEE802.3cd D2.1 Figure 91-8, using the variable and counter definitions from IEEE802.3cd 134.5.4 but modified for a single FEC lane operation.

### 5.5.10 Reed-Solomon decoder

#### 5.5.10.1 Overview

The Reed-Solomon decoder extracts the message symbols from the code word, correcting them as necessary, and discards the parity symbols. The message symbols correspond to 20 x 257-bit Transmission Words.

The Reed-Solomon decoder shall be capable of correcting any combination of up to t=715 symbol errors in a code word. It shall also be capable of indicating when a code word contains errors but was not corrected (e.g., it contains a number of errors in excess of the error correction capability).

#### 5.5.10.2 Link Degrade Signaling

For 64GFC links, Link Degrade Signaling can be supported by monitoring errors in the FEC logic. The Link Degrade Logic keeps track of the following parameters:

<u>FEC</u> Degrade interval – This is a 32 bit register that specifies the number of RS-FEC code words that make up a Degrade Interval. Bit 0 of this register is ignored so the number of FEC code words within a Degrade Interval is always even.

RD – Remote Degrade Bit to be sent in the Alignment Marker field.

<u>Degrade</u> Activate Threshold – This is a 32 bit register that specifies a symbol error count. The value here controls the threshold used to activate RD.

<u>Degrade Deactivate Threshold – This is a 32 bit register that specifies a symbol error count. The value here controls the threshold used to deactivate RD.</u>

The Reed Solomon Decoder counts the number of symbol errors detected in all the code words within the FEC degrade interval. If a codeword is uncorrectable, the number of symbol errors detected is incremented by 16. When the number of symbol errors detected within a FEC Degrade interval exceeds the FEC degrade activate threshold, RD(Remote Degrade) will be signaled to the remote link partner using a bit in the Alignment Marker. At the end of an interval, if the number of symbol errors is less than the FEC degrade deactivate threshold, RD will be de-asserted in the Alignment Marker.

# 5.5.11 Alignment marker removal

The first 257 message bits in every 1024th codeword is the vector am rxmapped<256:0> where bit 0 is the first bit received. The specific codewords that include this vector are indicated by the alignment lock function (see 5.5.9).

The vector am rxmapped shall be removed prior to transcoding.

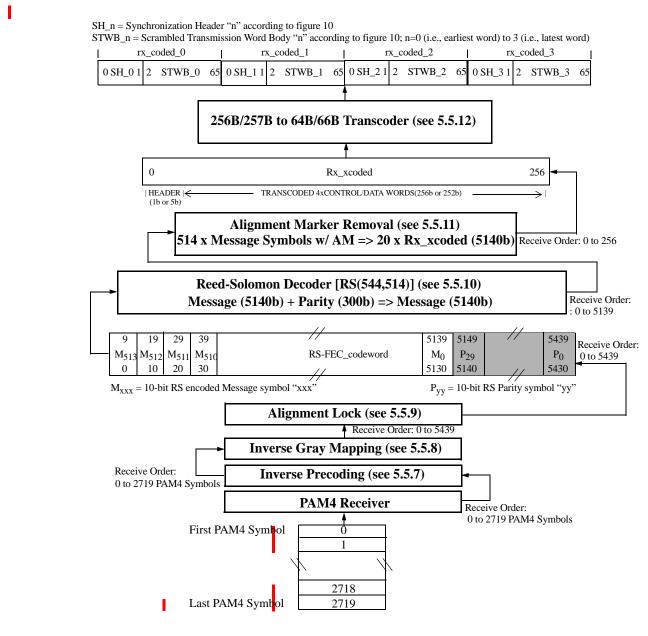

#### 5.5.12 64GFC 256B/257B to 64B/66B transcoder

The first five bits of the received block rx scrambled<256:0>, in reception order, are descrambled Rx scrambled<256:0> will yield rx coded<256:0> as follows:

- a) <u>set rx coded<4:0> to the result of the bit wise Exclusive-OR of rx scrambled<4:0> and rx scrambled<12:8>; and</u>

- b) set rx coded<256:5> to rx scrambled<256:5>.

Next, a group of four 66 bit transmission words are constructed from each received 257 bit transmission word as specified in 5.4.7.

The transcoder reconstructs a group of 4 x 66-bit Transmission Words from each received 257-bit Transmission Word.

The 4 x 66-bit Transmission Words, denoted as rx\_coded\_j<65:0> where j=0 to 3, shall be derived from each 257-bit Transmission Word rx\_xcoded<256:0> as defined in IEEE 802.3bj 2014 91.5.3.5. As the first 5 bits of rx\_xcoded<256:0> are not scrambled, the step defined in 802.3bj that derives rx\_xcoded from rx\_scrambled is not performed on those bits.

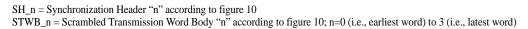

# 5.5.13 Transmit Bit Ordering

Transmit bit ordering for 64GFC 256B/257B is as shown in figure 24.

$SH_n = Synchronization Header "n" according to figure 10$  $STWB_n = Scrambled Transmission Word Body "n" according to figure 10; n=0 (i.e., earliest word) to 3 (i.e., latest word)$

Figure 24 - 64GFC 256B/257B transmit bit ordering

### 5.5.14 Receive Bit Ordering

Receive bit ordering for 64GFC 256B/257B is as shown in figure 25.

# 5.6 Transmitter Training Signal (TTS) for LSN and 32GFC/16GFC Transmitter Training

## 5.6.1 Overview

An FC-0 standard (e.g., FC-PI-5) may specify the use of the Transmitter Training Signal. The Transmitter Training Signal shall not be used for communication of Fibre Channel frames.

The Transmitter Training Signal is a transmission code that enables active feedback from a receiver to a transmitter to assist in adapting the transmitter to the characteristics of the link that connects them. Adjustable transmitter coefficients are supported. The use and effect of each coefficient is specified in FC-PI-x. It is expected that two FC\_Ports on a link will concurrently send the Transmitter Training Signal allowing each FC\_Port to evaluate the received signal quality and recommend adjustments to the transmitter of the other FC\_Port. The Transmitter Training Signal may be sent to communicate information without doing transmitter training.

The Transmitter Training Signal allows enabling of Forward Error Correction (FEC) (see 5.3). FEC is optional for 16GFC and mandatory for 32GFC. FEC negotiation is not performed for 32GFC links and 128GFC links (i.e., four parallel lanes of 32GFC in each direction). The Transmitter Training Signal allows enabling parallel lane support (see table 2) by setting Training Frame Control field bit 10 to one, if a lane is capable of running at 32GFC speeds.

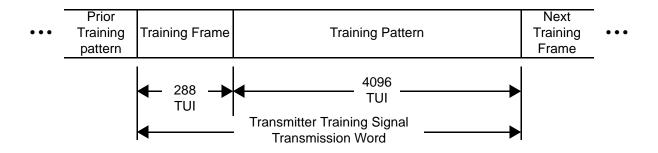

The Transmitter Training Signal shall be a repeating series of Transmission Words, each containing two elements (see figure 26):

- A Training Frame (see 5.6.2), which carries recommended adjustments to the transmitter of the receiving FC\_Port based on the quality of the signal detected at the receiver of the sending FC\_Port. The information in the Training Frame is encoded so as to increase its likelihood of reliable communication when the transmitter is not optimally adjusted for the link; and

- 2) A Training Pattern (see 5.6.3), which allows the receiving FC\_Port to formulate recommended adjustments to the transmitter of the sending FC\_Port. The Training Pattern is encoded so as to challenge the ability to reliably recover it when the transmitter is not optimally adjusted for the link.

Figure 26 - Transmitter Training Signal

### 5.6.2 Training Frame

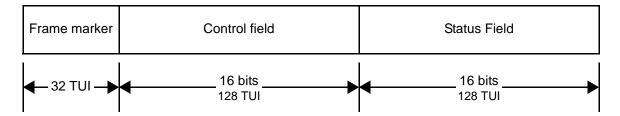

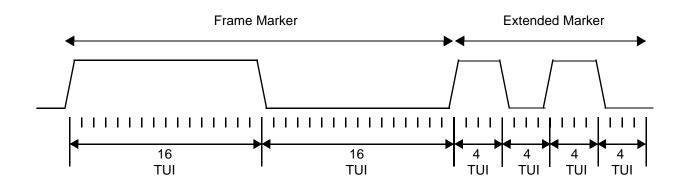

The Training Frame is the element of a Transmitter Training Signal that communicates training information from a receiver to a transmitter. A Training Frame comprises a 32 TUI frame marker followed by a 128 TUI Control field followed by a 128 TUI Status field (see figure 27).

NOTE Each bit of information in the Control field and the Status field is differential Manchester coded in an 8 TUI interval.

#### Figure 27 - Training Frame format

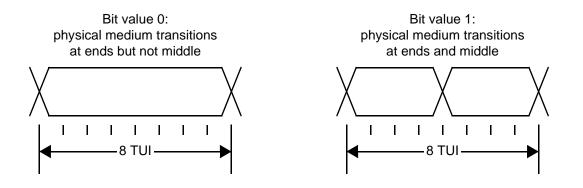

The Training Frame is intended to communicate information if the transmitter is not optimally adjusted for the link and the selected link speed. The Training Frame also carries information as to whether the physical interface supports parallel lanes and whether FEC is supported. Information in the Training Frame shall be encoded using differential Manchester coding at one eighth the nominal bit rate of the selected link speed (see figure 28).

NOTE Each bit of information in the Control field and the Status field is differential Manchester coded in an 8 TUI interval.

#### Figure 28 - Differential Manchester coding

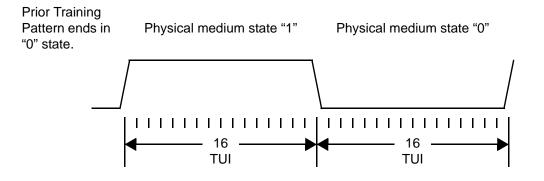

The beginning of a Training Frame shall be signaled by a frame marker. A frame marker shall be transmitted by holding the physical medium signal at logical "1" for 16 TUI followed by holding the physical medium at logical "0" for 16 TUI. This is a deliberate violation of one eighth rate differential Manchester coding, and carries no information (see figure 29).

Figure 29 - Frame marker signal

The Control field and the Status field each contain 16 bits of information (i.e., each contain 128 TUI of differential Manchester coded information). The information in these fields shall be transmitted so that more significant encoded information bits are transmitted before less significant encoded information bits. The electrical characteristics of the Transmitter Training Signal are specified in an FC-0 standard, and when indicated in this standard, are indicated informatively.

Figure 30 - 32GFC frame marker signal

An extended marker was specified in the Training Frame Control field for 32GFC since the 16GFC Training Frame Control field could be incorrectly recognized as the 32GFC frame marker and a 32GFC port could synchronize on the 16GFC Training Frame Control field. The extended marker is for 16 TUI as shown in figure 30 of alternating highs and lows to uniquely identify 32GFC. 32GFC locks onto the frame marker plus extended marker to preclude the potential of a false lock at 16GFC speeds. The extended marker shall be transmitted after the frame marker whenever a 32GFC Training Frame is transmitted.

Fields in the Control field shall be set as specified in table 2. Fields in the Status field shall be set as specified in table 3. See clause 9 For the use of these fields.

| Bits                    | Bits Field name Content  |                                                                                                                                                                                                                                                        |  |  |  |

|-------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15-14                   | Extended<br>Marker       | Set to 11b: Extended marker for 32GFC.<br>Set to 10b: reserved <u>Extended marker for 64GFC</u> .<br>Set to 01b: reserved.<br>Set to 00b: for 16GFC.                                                                                                   |  |  |  |

| 13                      | Preset                   | Set to one: the transmitter should set all coefficients to preset values.<br>Set to zero: no transmitter action advised.                                                                                                                               |  |  |  |

| 12                      | Initialize               | Set to one: The Transmitter should set all coefficients to initialize values.<br>Set to zero: no transmitter action.                                                                                                                                   |  |  |  |

| 11                      | FECReq                   | Set to one: the FC_Port is requesting the use of Forward Error<br>Correction (FEC) (see 5.3) in association with 64B/66B.<br>Set to zero: the FC_Port is directing not to use Forward Error<br>Correction (FEC) in association with 64B/66B.           |  |  |  |

| 10                      | Parallel Lane<br>Support | Set to one: parallel lanes are supported.<br>Set to zero: parallel lanes are not supported.                                                                                                                                                            |  |  |  |

| 9-6                     |                          | Reserved                                                                                                                                                                                                                                               |  |  |  |

| 5-4                     | C1Upd                    | Set to 11b: reserved.<br>Set to 10b: transmitter should decrement coefficient 1 one step. <sup>a</sup><br>Set to 01b: transmitter should increment coefficient 1 one step. <sup>a</sup><br>Set to 00b: transmitter should not change coefficient 1.    |  |  |  |

| 3-2                     | C0Upd                    | Set to 11b: reserved.<br>Set to 10b: transmitter should decrement coefficient 0 one step. <sup>a</sup><br>Set to 01b: transmitter should increment coefficient 0 one step. <sup>a</sup><br>Set to 00b: transmitter should not change coefficient 0.    |  |  |  |

| 1-0                     | C-1Upd                   | Set to 11b: reserved.<br>Set to 10b: transmitter should decrement coefficient -1 one step. <sup>a</sup><br>Set to 01b: transmitter should increment coefficient -1 one step. <sup>a</sup><br>Set to 00b: transmitter should not change coefficient -1. |  |  |  |

| <sup>a</sup> See FC-PI- | 5.                       |                                                                                                                                                                                                                                                        |  |  |  |

|--|

\_

| Bits          | Field name | Content                                                                                                                                                             |

|---------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15            | тс         | Set to one: transmitter training is complete.<br>Set to zero: request to begin or continue transmitter training.                                                    |

| 14            | SN         | Set to one: the transmitter is using and has not completed<br>Speed Negotiation.<br>Set to zero: the transmitter has completed or did not use Speed<br>Negotiation. |

| 13            | FECCap     | Set to one: FC_Port has Forward Error Correction (FEC)<br>capability (see 5.3).<br>Set to zero: FC_Port does not have Forward Error Correction<br>(FEC) capability. |

| 12            | TF         | Set to one: the transmitter is operating with fixed transmitter coefficients.<br>Set to zero: the transmitter coefficients may be trained by the receiver.          |

| 11-6          |            | Reserved                                                                                                                                                            |

| 5-4           | C1Stat     | Set to 11b: transmitter coefficient 1 acknowledges an update                                                                                                        |

|               |            | that left it at its maximum value. <sup>a</sup><br>Set to 10b: transmitter coefficient 1 acknowledges an update                                                     |

|               |            | that left it at its minimum value. <sup>a</sup><br>Set to 01b: transmitter coefficient 1 acknowledges an update                                                     |

|               |            | that is complete. <sup>a</sup><br>Set to 00b: transmitter coefficient 1 is ready for another update.                                                                |

| 3-2           | C0Stat     | Set to 11b: transmitter coefficient 0 acknowledges an update<br>that left it at its maximum value.<br>Set to 10b: transmitter coefficient 0 acknowledges an update  |

|               |            | that left it at its minimum value. <sup>a</sup><br>Set to 01b: transmitter coefficient 0 acknowledges an update                                                     |

|               |            | that is complete. <sup>a</sup><br>Set to 00b: transmitter coefficient 0 is ready for another update.                                                                |

| 1-0           | C-1Stat    | Set to 11b: transmitter coefficient -1 acknowledges an update                                                                                                       |

|               |            | that left it at its maximum value. <sup>a</sup><br>Set to 10b: transmitter coefficient -1 acknowledges an update                                                    |

|               |            | that left it at its minimum value. <sup>a</sup><br>Set to 01b: transmitter coefficient -1 acknowledges an update                                                    |

|               |            | that is complete. <sup>a</sup><br>Set to 00b: transmitter coefficient -1 is ready for another<br>update.                                                            |

| a See FC-PI-5 | 5.         |                                                                                                                                                                     |

|               |            |                                                                                                                                                                     |

| Table 3 - Training Frame Status field |

|---------------------------------------|

|---------------------------------------|

# 5.6.3 Training Pattern

The Training Pattern is the element of a Transmitter Training Signal that allows a receiver to evaluate its ability to achieve reliable Fibre Channel communication across the link on which the Training Pattern is sent. The Training Pattern shall be composed of 4094 TUI of PRBS-11 followed by two TUI of zero. PRBS-11 (see figure 31) shall be equivalent to the output of an 11-bit linear feedback shift register that is initialized to a value that is randomized to a non-zero value for each training frame, and that implements the polynomial

$x^{11} + x^9 + 1$

Figure 31 - PRBS-11 as a linear feedback shift register

# 5.7 Transmitter Training Signal (TTS) for 64GFC Transmitter Training

The training frame structure is specified in IEEE 802.3-2015 136.8.11.1.

The training frame marker is specified in IEEE 802.3-2015 136.8.11.1.1.

Control and status field behavior is specified in IEEE 802.3-2015 136.8.11.1.2. The Control field is specified in table 4.

| <u>Bits</u>  | Field name                             | Content                                                                                                                             |  |  |  |

|--------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <u>15-14</u> | Extended<br>Marker                     | Set to 11b: Extended marker for 32GFC.<br>Set to 10b: Extended marker for 64GFC.<br>Set to 01b: reserved.<br>Set to 00b: for 16GFC. |  |  |  |

| <u>13-12</u> | Initial Condi-<br>tion request         | Set to 11b: Preset 3.<br>Set to 10b: Preset 2.<br>Set to 01b: Preset 1.<br>Set to 00b: Individual Coefficient Control.              |  |  |  |

| <u>11</u>    | <u>Reserved</u>                        | Transmit as zero, ignore on receipt.                                                                                                |  |  |  |

| <u>10</u>    | Parallel Lane                          | Set to one: parallel lanes are supported.<br>Set to zero: parallel lanes are not supported.                                         |  |  |  |

| <u>9-8</u>   | Modulation<br>and Precoding<br>request | Set to 11b: PAM4 with precoding.<br>Set to 10b: PAM4<br>Set to 01b: reserved<br>Set to 00b: PAM2.                                   |  |  |  |

| <u>7-5</u>   | <u>Reserved</u>                        | Transmit as zero, ignore on receipt.                                                                                                |  |  |  |

| <u>4-2</u>   | <u>Coefficient</u><br><u>Select</u>    | Set to 110b: c(-2)           Set to 111b: c(-1)           Set to 000b: c(0)           Set to 001b: c(1)                             |  |  |  |

| <u>1-0</u>   | <u>Coefficient</u><br><u>Request</u>   | Set to 11b: No equalization<br>Set to 10b: Decrement<br>Set to 01b: Increment<br>Set to 00b: Hold                                   |  |  |  |

| а            |                                        |                                                                                                                                     |  |  |  |

Table 4 - 64GFC Training Frame Control field

The Status field is specified in table 5.

| <u>Bits</u>  | Field name                            | Content                                                                                                                                                                                                                                                                    |  |  |  |

|--------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <u>15</u>    | <u>Receiver</u><br><u>Ready</u>       | Set to one: training is complete and receiver is ready for data.<br>Set to zero: request for Training to continue.                                                                                                                                                         |  |  |  |

| <u>14</u>    | <u>SN</u>                             | Set to one: transmitter has not completed LSN.<br>Set to zero: transmitter has completed LSN.                                                                                                                                                                              |  |  |  |

| <u>13</u>    | <u>Reserved</u>                       | Transmit as zero, ignore on receipt.                                                                                                                                                                                                                                       |  |  |  |

| <u>12</u>    | ŢĒ                                    | Set to one: transmitter is operating with Fixed Coefficients.<br>Set to zero: transmitter coefficients may be trained by the receiver.                                                                                                                                     |  |  |  |

| <u>11-10</u> | Modulation<br>and Precoding<br>Status | Set to 11b: PAM4 with precoding.<br>Set to 10b: PAM4.<br>Set to 01b: reserved<br>Set to 00b: PAM2                                                                                                                                                                          |  |  |  |

| <u>9</u>     | <u>Receiver</u><br>frame lock         | Set to one: frame boundaries identified.<br>Set to zero: frame boundaries not identified.                                                                                                                                                                                  |  |  |  |

| <u>8</u>     | Initial Condi-<br>tion Status         | <u>Set to one: updated.</u><br><u>Set to zero: not updated.</u>                                                                                                                                                                                                            |  |  |  |

| <u>7</u>     | <u>Parity</u>                         | Parity bit to provide DC balance.                                                                                                                                                                                                                                          |  |  |  |

| <u>6</u>     | <u>Reserved</u>                       | Transmit as zero, ignore on receipt.                                                                                                                                                                                                                                       |  |  |  |

| <u>5-3</u>   | Coefficient<br>Select Echo            | <u>Set to 110b: c(-2)</u><br><u>Set to 111b: c(-1)</u><br><u>Set to 000b: c(0)</u><br><u>Set to 001b: c(1)</u>                                                                                                                                                             |  |  |  |

| <u>2-0</u>   | <u>Coefficient</u><br><u>Status</u>   | Set to 111b: reserved<br>Set to 110b: coefficient at limit and maximum voltage<br>Set to 101b: reserved<br>Set to 100b: maximum voltage<br>Set to 011b: coefficient not supported<br>Set to 010b: coefficient at limit<br>Set to 001b: updated<br>Set to 000b: not updated |  |  |  |

Table 5 - 64GFC Training Frame Status field

The training pattern is specified in IEEE 802.3-2015 136.8.11.1.3.

The zero pad is specified in IEEE 802.3-2015 136.8.11.1.4.

# 5.8 FEC for 128GFC

# 5.8.1 Overview

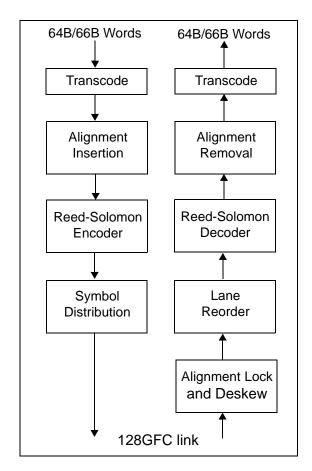

This clause specifies how Forward Error Correction (FEC) is implemented on 128GFC ports. FEC usage is mandatory on 128GFC ports. Streams of 64/66B Transmission Words in both directions on a 128GFC link are encoded by the FEC layer as specified below.

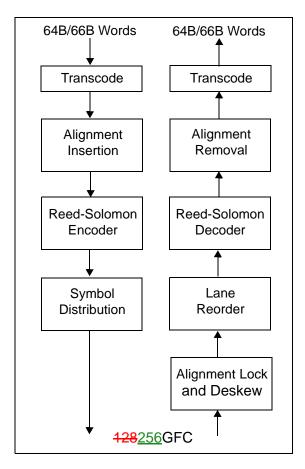

# 5.8.2 Functional block diagram

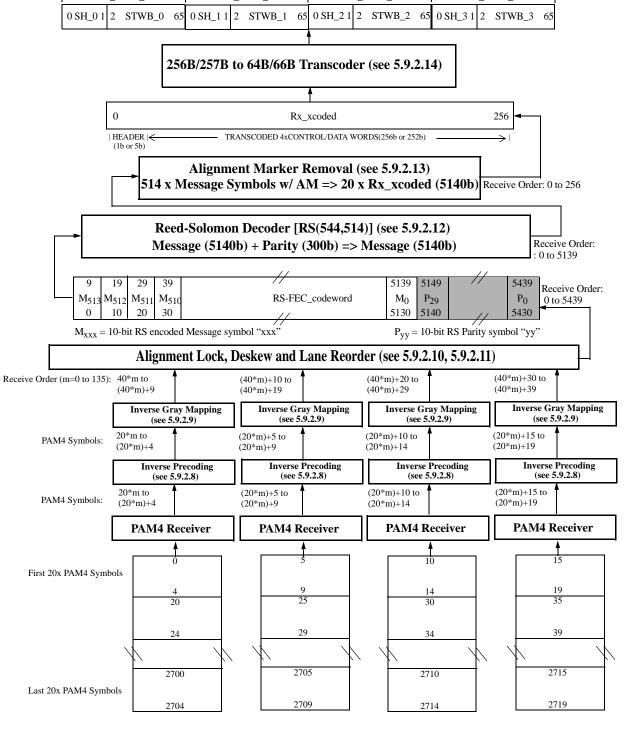

A functional block diagram of the 128GFC RS-FEC sub layer is shown in figure 32.

Figure 32 - 128GFC RS-FEC sub layer functional block diagram

# 5.8.2.1 64B/66B to 256B/257B Transcoder

Transcoding is done as specified in 5.4.2.

In addition, as a final step, the first five bits are scrambled in transmission order as specified in IEEE 802.3bj-2014 91.5.2.5.

After this step, tx\_xcoded<256:0> will yield tx\_scrambled<256:0> as follows:

- a) Set tx\_scrambled<4:0> to the result of the bit wise Exclusive-OR of tx\_xcoded<4:0> and tx\_xcoded <12:8>; and

- b) Set tx\_scrambled<256:5> to tx\_xcoded<256:5>.

#### 5.8.2.2 Alignment marker mapping and insertion

The alignment insertion function inserts a unique data pattern (i.e., Alignment Marker) for each link into the data stream to enable identification of which of the four links is which FEC lane. This function enables the receiver to map the physical links to logical lanes allowing for random connections of the Transmit links to the Receive links within the group of 4 links, in addition to providing a framing pattern for aligning the FEC code words.

The first 514b of every 4096<sup>th</sup> FEC code word carries Alignment Marker information.

The alignment marker bit sequence is identical to the first two re-mapped AM TC blocks specified in Clause 82.2.7 and Clause 91.5.2.6 when replacing the BIP3 field in all four instances of the AM0 blocks with the value 0xCA, the BIP3 for AM4 with 0x9D, the BIP3 for AM5 with 0xD7, the BIP3 for AM6 with 0x6F, and the BIP3 for AM7 with 0xA1. Additionally the first bit of AM8 and AM9 that are part of the sequence is changed from 0->1 to maintain DC balance.

Table 6 shows the data stream that will appear on each of the 4 lanes after the RS symbol distribution of the AM pattern is done. The 'd' is the first 6b of data from TC block that follows the AM pattern. The underlined values are the replaced BIP3 and BIP7 fields in the AM blocks.

| AM bits   | Lane3              | Lane2              | Lane1              | Lane0              |

|-----------|--------------------|--------------------|--------------------|--------------------|

| [39:0]    | 0011000001         | 0011000001         | 0011000001         | 0011000001         |

| [79:40]   | 0001011010         | 0001011010         | 0001011010         | 0001011010         |

| [119:80]  | <u>001010</u> 0010 | <u>001010</u> 0010 | <u>001010</u> 0010 | <u>001010</u> 0010 |

| [159:120] | 00111110 <u>11</u> | 00111110 <u>11</u> | 00111110 <u>11</u> | 00111110 <u>11</u> |

| [199:160] | 1010010111         | 1010010111         | 1010010111         | 1010010111         |

| [239:200] | <u>0101</u> 110111 | <u>0101</u> 110111 | <u>0101</u> 110111 | <u>0101</u> 110111 |

| [279:240] | 111011 <u>0011</u> | 011010 <u>0011</u> | 011101 <u>0011</u> | 110101 <u>0011</u> |

| [319:280] | 0100010101         | 0100101010         | 0001010011         | 0000011111         |

| [359:320] | <u>01</u> 01100110 | <u>11</u> 00100110 | <u>11</u> 11000010 | <u>01</u> 00001001 |

| [399:360] | 0100 <u>101000</u> | 0101 <u>011011</u> | 0010 <u>110101</u> | 1010 <u>100111</u> |

| [439:400] | 1110101000         | 1101010110         | 1010110010         | 1110000000         |

| [479:440] | 1001100110         | 1101100110         | 0011110111         | 1111011011         |

| [513:480] | ddddd <u>1110</u>  | 01 <u>10010000</u> | 01 <u>00101000</u> | 01 <u>01100010</u> |

#### Table 6 - 128GFC FEC Alignment Marker

#### 5.8.2.3 Reed-Solomon encoder

Reed-Solomon encoding is done as specified in 5.4.3.

#### 5.8.2.4 Symbol distribution

Once the data has been encoded, it is distributed to 4 lanes, in groups of 10 bit symbols.

Symbol distribution is done as specified in IEEE 802.3bj-2014 91.5.2.8.

#### 5.8.2.5 Transmit bit ordering

Transmit bit ordering is as shown in figure 33.

### 5.8.2.6 Alignment lock and deskew

The receive function creates 4 bit streams after concatenating the bits received on each lane. It then obtains LOCK to the alignment markers on each lane as specified by the FEC synchronization state diagram in IEEE802.3bj-2014 91.5.3.1.

After alignment marker lock is achieved on all four lanes, all inter lane skew is removed as specified by the FEC alignment state diagram in IEEE802.3bj-2014 91.5.3.1. The FEC receive function will support a maximum skew of 180ns between lanes and a maximum skew variation of 4ns.

### 5.8.2.7 Lane reorder

FEC lanes may be received on different lanes of the service interface from which they were originally transmitted.

The FEC receive function shall order the FEC lanes according to the FEC lane number per IEEE802.3bj-2014-91.5.3.2.The FEC lane number is defined by the alignment marker that is mapped to each FEC lane.

After all FEC lanes are aligned, deskewed, and reordered, the FEC lanes are multiplexed together in the proper order to reconstruct the original stream of FEC code words.

# 5.8.2.8 Reed-Solomon decoder

Decoding is done as specified in 5.4.6.

#### 5.8.2.9 Alignment marker removal

The first 514 bits in every 4096 code words are the mapped alignment marker bits. These are removed before sending the data to the transcode block.

# 5.8.2.10 256B/257B to 64B/66B transcoder

The first five bits of the of the received block rx\_scrambled<256:0>, in reception order, are descrambled. Rx\_scrambled<256:0> will yield rx\_coded<256:0> as follows:

- a) Set rx\_coded<4:0> to the result of the bit wise Exclusive-OR of rx\_scrambled<4:0> and rx\_scrambled<12:8>; and

- b) Set rx\_coded<256:5> to rx\_scrambled<256:5>.

Next, a group of four 66bit transmission words are constructed from each received 257 bit transmission word as specified in 5.4.7.

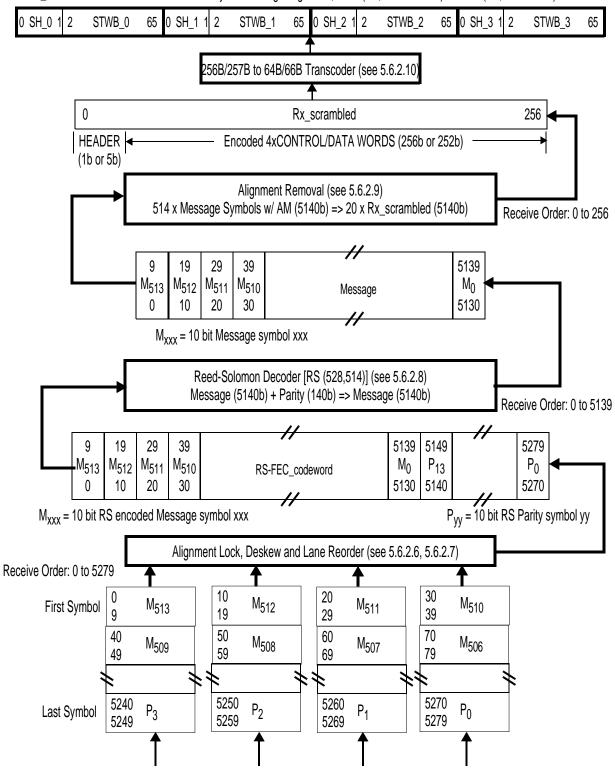

# 5.8.2.11 Receive bit ordering

Receive bit ordering is as specified in figure 34.

# SH\_n = Synchronization Header n according to figure 10

STWB\_n = Scrambled Transmission Word Body n according to figure 10; n = 0 (i.e., earliest word) to n = 3 (i.e., latest word)

Figure 33 - Transmit bit ordering

# SH\_n = Synchronization Header n according to figure 10

STWB\_n = Scrambled Transmission Word Body n according to figure 10; n = 0 (i.e., earliest word) to n = 3 (i.e., latest word)

Figure 34 - Receive bit ordering

# 5.9 FEC for 256GFC

## 5.9.1 Overview

This clause specifies how Forward Error Correction (FEC) is implemented on <u>128256</u>GFC ports. FEC usage is mandatory on <u>128256</u>GFC ports. Streams of 64/66B Transmission Words in both directions on a <u>128256</u>GFC link are encoded by the FEC layer as specified below.

### 5.9.2 Functional block diagram

A functional block diagram of the <u>128</u>256GFC RS-FEC sub layer is shown in figure 35.

Figure 35 - 128256GFC RS-FEC sub layer functional block diagram

#### 5.9.2.1 64B/66B to 256B/257B Transcoder

64B/66B to 256B/257B transcoding is done as specified in 5.8.2.1.

Transcoding is done as specified in 5.4.2.

In addition, as a final step, the first five bits are scrambled in transmission order as specified in IEEE 802.3bj 2014 91.5.2.5.

After this step, tx\_xcoded<256:0> will yield tx\_scrambled<256:0> as follows:

- a) Set tx\_scrambled<4:0> to the result of the bit wise Exclusive OR of tx\_xcoded<4:0> and tx\_xcoded <12:8>; and

- b) Set tx\_scrambled<256:5> to tx\_xcoded<256:5>.

#### 5.9.2.2 Alignment marker mapping and insertion

The alignment insertion function inserts a unique data pattern (i.e., Alignment Marker) for each link into the data stream to enable identification of which of the four links is which FEC lane. This function enables the receiver to map the physical links to logical lanes allowing for random connections of the Transmit links to the Receive links within the group of 4 links, in addition to providing a framing pattern for aligning the FEC code words.

The first 514b of every 4096<sup>th</sup> FEC code word carries Alignment Marker information.

The alignment marker bit sequence is identical to the first two re-mapped AM TC blocks specified in Clause 82.2.7 and Clause 91.5.2.6 when replacing the BIP3 field for Lane 1, Lane 2, and Lane 3 in all four instances of the AM0 blocks with the value 0xCA, the BIP3 for AM4 with 0x9D, the BIP3 for AM5 with 0xD7, the BIP3 for AM6 with 0x6F, and the BIP3 for AM7 with 0xA1. For Lane0, the BIP3 field of AM0 carries Link degrade information associated with the link degrade function (see 5.5.10.2). Additionally the first bit of AM8 and AM9 that are part of the sequence is changed from 0->1 to maintain DC balance.

Table 7 shows the data stream that will appear on each of the 4 lanes after the RS symbol distribution of the AM pattern is done. The 'd' is the first 6b of data from TC block that follows the AM pattern. The underlined values are the replaced BIP3 and BIP7 fields in the AM blocks.

| AM bits   | Lane3              | Lane2              | Lane1              | Lane0                                                 |

|-----------|--------------------|--------------------|--------------------|-------------------------------------------------------|

| [39:0]    | 0011000001         | 0011000001         | 0011000001         | 0011000001                                            |

| [79:40]   | 0001011010         | 0001011010         | 0001011010         | 0001011010                                            |

| [119:80]  | <u>001010</u> 0010 | <u>001010</u> 0010 | <u>001010</u> 0010 | <u>10000,</u><br><u>RD,<del>001010</del></u> 00<br>10 |

| [159:120] | 00111110 <u>11</u> | 00111110 <u>11</u> | 00111110 <u>11</u> | 00111110 <u><del>11</del>10</u>                       |

| [199:160] | 1010010111         | 1010010111         | 1010010111         | 1010010111                                            |

| [239:200] | <u>0101</u> 110111 | <u>0101</u> 110111 | <u>0101</u> 110111 | <u>0101</u> 111,<br><u>~RD,</u> 110111                |

| [279:240] | 111011 <u>0011</u> | 011010 <u>0011</u> | 011101 <u>0011</u> | 110101 <u>00110</u><br><u>101</u>                     |

| [319:280] | 0100010101         | 0100101010         | 0001010011         | 0000011111                                            |

| [359:320] | <u>01</u> 01100110 | <u>11</u> 00100110 | <u>11</u> 11000010 | <u>01</u> 00001001                                    |

| [399:360] | 0100 <u>101000</u> | 0101 <u>011011</u> | 0010 <u>110101</u> | 1010 <u>100111</u>                                    |

| [439:400] | 1110101000         | 1101010110         | 1010110010         | 1110000000                                            |

| [479:440] | 1001100110         | 1101100110         | 0011110111         | 1111011011                                            |

| [513:480] | dddddd <u>1110</u> | 01 <u>10010000</u> | 01 <u>00101000</u> | 01 <u>01100010</u>                                    |

#### Table 7 - 128256GFC FEC Alignment Marker

## 5.9.2.3 Reed-Solomon encoder

Reed-Solomon encoding is done as specified in 5.5.4.

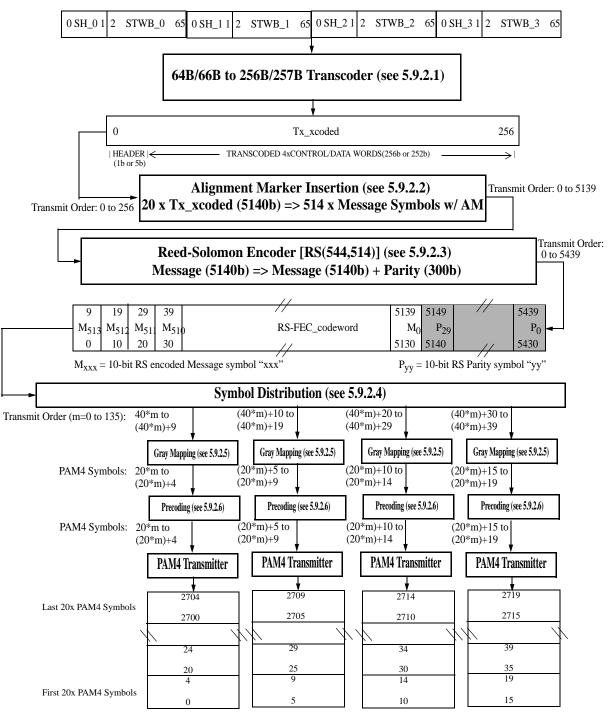

### 5.9.2.4 Symbol distribution

Once the data has been encoded, it is distributed to 4 lanes, in groups of 10 bit symbols.

Symbol distribution is done as specified in IEEE 802.3bj-2014 91.5.2.8.

# 5.9.2.5 Gray mapping

Gray mapping is done as specified in 5.5.5.

# 5.9.2.6 Precoding

Precoding is done as specified in 5.5.6.

## 5.9.2.7 Transmit bit ordering

Transmit bit ordering is as shown in figure 36.

Figure 36 - 25GFC 256B/257B transmit bit ordering

#### 5.9.2.8 Inverse precoding

Inverse precoding is done as specified in 5.5.7.

#### 5.9.2.9 Inverse Gray mapping

Inverse Gray mapping is done as specified in 5.5.8.

#### 5.9.2.10 Alignment lock and deskew

The receive function creates 4 bit streams after concatenating the bits received on each lane. It then obtains LOCK to the alignment markers on each lane as specified by the FEC synchronization state diagram in IEEE802.3bj-2014 91.5.3.1.

After alignment marker lock is achieved on all four lanes, all inter lane skew is removed as specified by the FEC alignment state diagram in IEEE802.3bj-2014 91.5.3.1. The FEC receive function will support a maximum skew of 180ns between lanes and a maximum skew variation of 4ns.

#### 5.9.2.11 Lane reorder

FEC lanes may be received on different lanes of the service interface from which they were originally transmitted.

The FEC receive function shall order the FEC lanes according to the FEC lane number per IEEE802.3bj-2014-91.5.3.2.The FEC lane number is defined by the alignment marker that is mapped to each FEC lane.

After all FEC lanes are aligned, deskewed, and reordered, the FEC lanes are multiplexed together in the proper order to reconstruct the original stream of FEC code words.

#### 5.9.2.12 Reed-Solomon decoder

Decoding is done as specified in 5.5.10.1. In addition, link degrade signaling is done as specified in 5.5.10.2.

#### 5.9.2.13 Alignment marker removal

The first 514 bits in every 4096 code words are the mapped alignment marker bits. These are removed before sending the data to the transcode block.

### 5.9.2.14 256B/257B to 64B/66B transcoder

The first five bits of the of the received block rx\_scrambled<256:0>, in reception order, are descrambled. Rx\_scrambled<256:0> will yield rx\_coded<256:0> as follows:

- a) Set rx\_coded<4:0> to the result of the bit wise Exclusive-OR of rx\_scrambled<4:0> and rx\_scrambled<12:8>; and

- b) Set rx\_coded<256:5> to rx\_scrambled<256:5>.

Next, a group of four 66bit transmission words are constructed from each received 257 bit transmission word as specified in 5.4.7.

# 5.9.2.15 Receive bit ordering

Receive bit ordering is as specified in figure 37.

Figure 37 - 256GFC 256B/257B receive bit ordering

# **6 FC-1 Transmission Word Synchronization**

# 6.1 Scope

I

Transmission Word Synchronization is a function of the FC-1 level.

# 6.2 Introduction

In the Fibre Channel architecture, the FC-0 level is responsible for bit transmission and reception (see FC-PI-x). The FC-1 level is responsible for providing a stream of bits for the FC-0 level to transmit. No state information is needed to accomplish this other than that necessary for 64B/66B scrambling and 8B/10B running disparity. The FC-1 level is also responsible for deriving Transmission Word Synchronization and Transmission Words from the received bit stream.

Whenever a signal (see FC-PI-x) is detected on a fibre, the receiver attached to that fibre shall attempt to achieve synchronization on both bit and Transmission Word boundaries of the received encoded bit stream. Bit Synchronization is defined in FC-PI-x. Transmission Word Synchronization is defined in this clause. Synchronization failures on either bit or Transmission Word boundaries are not separately identifiable; both cause Loss-of-Synchronization errors.

An FC\_Port receiver has two mutually exclusive receiver Transmission Word Synchronization states, Word Synchronization Acquired and Loss of Synchronization. In the Word Synchronization Acquired state, the FC-1 level shall decode the received signal and pass information to the FC-2P level. In the Loss of Synchronization state, the FC-1 level shall not pass information to the FC-2P level.

A receiver may provide an indication of a Loss-of-Signal condition (see FC-PI-x).

# 6.3 8B/10B Transmission Word Synchronization

# 6.3.1 State Diagram Overview

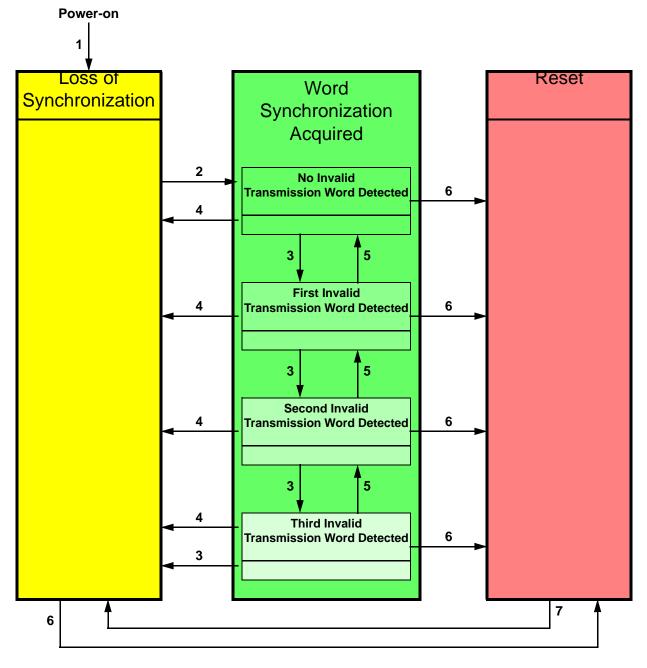

The Receiver State Diagram for 8B/10B Transmission Word Synchronization is shown in figure 39.

The Receiver states are as follows:

- a) Loss of Synchronization state;

- b) No Invalid Transmission Word Detected state;

- c) First Invalid Transmission Word Detected state;

- d) Second Invalid Transmission Word Detected state;

- e) Third Invalid Transmission Word Detected state; and

- f) Reset state.

Being in one of the Word Synchronization Acquired states refers to being in any of:

- a) No Invalid Transmission Word Detected state;

- b) First Invalid Transmission Word Detected state;

- c) Second Invalid Transmission Word Detected state; or

- d) Third Invalid Transmission Word Detected state.

The receiver state transitions are defined as follows:

a) Transition 1: Power-on;

I

- b) Transition 2: Acquisition of Word Synchronization (see 6.3.3.2.2);

- c) Transition 3: An invalid Transmission Word is detected (see 6.3.4.2);

- d) Transition 4: A detection of a Loss-of-Signal condition (see 6.2);

- e) Transition 5: Two consecutive Transmission Words that are not Invalid Transmission Words are detected (see 6.3.4.2);

- f) Transition 6: Reset condition imposed on the receiver (see 6.3.5.4); and

- g) Transition 7: Exiting of receiver reset condition (see 6.3.5.4).

Figure 39 - Receiver state diagram

# 6.3.2 Operational and not operational conditions

When the receiver is operational, it shall be in either the Loss of Synchronization state or in one of the Word Synchronization Acquired states.

When the receiver is Not operational, it shall be in the Reset state.

# 6.3.3 Transmission Word Synchronization Procedure

The Transmission Word Synchronization procedure consists of first achieving Bit Synchronization (see 6.3.3.1), followed by achieving Transmission Word Synchronization (see 6.3.3.2).

# 6.3.3.1 Bit Synchronization

I

An operational receiver that is in the Loss of Synchronization state shall first acquire Bit Synchronization before attempting to acquire Transmission Word Synchronization. Bit Synchronization is defined in FC-PI-x. After achieving Bit Synchronization, the receiver shall remain in the Loss of Synchronization state until it achieves Transmission Word Synchronization.

# 6.3.3.2 Transmission Word Synchronization detection

# 6.3.3.2.1 Introduction

The comma contained within the K28.5 special character is a singular bit pattern that in the absence of transmission errors shall not appear in any other location of a Transmission Character and shall not be generated across the boundaries of any two adjacent Transmission Characters. This bit pattern is sufficient to identify the Transmission Word alignment of the received bit stream. Some implementations (e.g., those that choose to implement the Transmission Word alignment function in Continuous-mode alignment) may choose to align on the full K28.5 Ordered Set to decrease the likelihood of false alignment when bit errors are present in the received bit stream.

Placement of a K28.5 Transmission Character at the left-most position of a received Transmission Word ensures proper alignment of that Transmission Word and of subsequently received Transmission Words. Ordered Set detection shall include both detection of the individual Transmission Characters that make up an Ordered Set and proper alignment of those characters (i.e., the Special Character used to designate an Ordered Set shall be aligned in the leading (left-most) character position of the received Transmission Word).

# 6.3.3.2.2 Achieving Transmission Word Synchronization

A receiver that is in the Loss of Synchronization state and has acquired Bit Synchronization shall attempt to acquire Transmission Word Synchronization. Transmission Word Synchronization is acquired by the detection of three Ordered Sets containing commas in their left-most bit positions without an intervening invalid Transmission Word, as specified in 6.3.4.2. The third detected Ordered Set shall change the state from the Loss of Synchronization state to the No Invalid Transmission Word Detected state using transition 2. The third detected Ordered Set shall be considered valid information and shall be decoded and provided by the receiver to its FC\_Port. A receiver in any of the Word Synchronization Acquired states shall provide information that has been received from its attached fibre and decoded.

The method used by the receiver to implement the Transmission Word alignment function and to detect Ordered Sets is not defined by this standard.

# 6.3.3.2.3 8B/10B Transmission Word Synchronization for speed negotiation

If the link speed negotiation algorithm (see 8.6) is performed using 8B/10B, then the pass sync\_test count shall be 1 000.

# 6.3.3.2.4 Transmission Word alignment methods

# 6.3.3.2.4.1 Continuous-mode alignment

Continuous-mode alignment allows the receiver to reestablish Transmission Word alignment at any point in the incoming bit stream while the receiver is operational. Such realignment is likely (but not guaranteed) to result in code violations and subsequent Loss-of-Synchronization. Under certain conditions, it may be possible to realign an incoming bit stream without Loss-of-Synchronization. If such a realignment occurs within a received frame, detection of the resulting error condition is dependent upon higher-level function (e.g., invalid CRC, missing EOF Delimiter).

# 6.3.3.2.4.2 Explicit-mode alignment

Explicit-mode alignment allows the receiver to reestablish Transmission Word alignment under controlled circumstances (e.g., while in the Loss of Synchronization State). Once synchronization has been acquired, the Transmission Word alignment function of the receiver is disabled.

### 6.3.4 Loss of Transmission Word Synchronization

### 6.3.4.1 Introduction

I

Loss of Transmission Word Synchronization shall occur in the following conditions:

- a) a Loss-of-Signal is detected when in any of the Word Synchronization Acquired states; or

- b) an invalid Transmission Word is detected in the Third Invalid Transmission Word Detected state.

### 6.3.4.2 Detection of an invalid Transmission Word

In each of the Word Synchronization Acquired states each received Transmission Word is tested to determine the validity of the Transmission Word.

An invalid Transmission Word shall be recognized by the receiver when one of the following conditions is detected:

- a) a code violation, as specified by the 8B/10B transmission code (see 5.2), is detected within a Transmission Word. This is referred to as a code violation condition;

- b) a K30.7 special character is detected in any character position of a Transmission Word. This indicates an error condition has been detected at a lower implementation level within the receiver;

- c) any valid special character is detected in the second, third, or fourth character position of a Transmission Word. This is referred to as an invalid special code alignment condition; or

- d) a defined Ordered Set (see clause 5) is received with improper beginning running disparity (e.g., a SOF delimiter is received with positive beginning running disparity, an EOF delimiter specified for positive beginning running disparity is received when beginning running disparity for that Transmission Word is negative). This is referred to as an invalid beginning running disparity condition.

#### 6.3.5 State transitions

# 6.3.5.1 Default State

A receiver shall enter the Loss of Synchronization state on power-on (i.e., default).

### 6.3.5.2 Loss of Synchronization state

I

The Loss of Synchronization State shall be entered upon the following conditions:

- a) completion of the Loss-of-Synchronization procedure while in the Third Invalid Transmission Word Detected state using transition 3;

- b) detection of Loss-of-Signal while in the No Invalid Transmission Word Detected state, the First Invalid Transmission Word Detected state, the Second Invalid Transmission Word Detected state, or the Third Invalid Transmission Word Detected state using transition 4; or

- c) completion of the reset while in the Reset state using transition 7.

While in the Loss of Synchronization State, the receiver may attempt to reacquire Bit Synchronization. In some instances, this may allow the receiver to regain Transmission Word Synchronization when it otherwise would not be possible. However, initiation of bit re synchronization may also delay the synchronization process by forcing the receiver to reestablish a clock reference when such reestablishment is otherwise unnecessary (see FC-PI-x for a detailed discussion of Bit Synchronization).

When Transmission Word Synchronization is acquired the receiver shall enter the No Invalid Transmission Word Detected state using transition 2. Imposing a reset condition upon the receiver shall cause any state to transition to the Reset state using transition 6.

### 6.3.5.3 Word Synchronization Acquired states

### 6.3.5.3.1 Loss-of-Synchronization procedure

The following four states are defined as Word Synchronization Acquired states:

- a) No Invalid Transmission Word Detected state;

- b) First Invalid Transmission Word Detected state;

- c) Second Invalid Transmission Word Detected state; or

- d) Third Invalid Transmission Word Detected state.

NOTE 10 - The rationale for the Loss-of-Synchronization procedure is to reduce the likelihood that a single error results in a Loss-of-Synchronization. A single two-bit error positioned to overlap two Transmission Words could result in the detection of three invalid Transmission Words; the two Transmission Words directly affected by the error and a subsequent Transmission Word that was affected by a disparity change resulting from the error. The procedure described above would maintain synchronization in such a case.

#### 6.3.5.3.2 No Invalid Transmission Word Detected state

When the procedure is in the No Invalid Transmission Word Detected state, checking for an invalid Transmission Word shall be performed. Any invalid Transmission Word shall cause the No Invalid Transmission Word Detected state to transition to the First Invalid Transmission Word Detected state (transition 3). A Loss-of-Signal condition shall cause the No Invalid Transmission Word Detected state to transition to the Loss of Synchronization state (transition 4). A reset condition imposed upon the receiver shall cause the No Invalid Transmission Word Detected state to transition 4).

# 6.3.5.3.3 First Invalid Transmission Word Detected state

When the procedure is in the First Invalid Transmission Word Detected state, checking for an invalid Transmission Word shall be performed. Any invalid Transmission Word shall cause the First Invalid Transmission Word Detected state to transition to the Second Invalid Transmission Word Detected state (transition 3). If two consecutive Transmission Words that are not Invalid Transmission Words are received, the First Invalid Transmission Word Detected state (transition 5). A Loss-of-Signal condition shall cause the First Invalid Transmission Word Detected state to transition to the Loss of Synchronization state (transition 4). A reset condition imposed upon the receiver shall cause the First Invalid Transmission to the Reset state (transition 6).

### 6.3.5.3.4 Second Invalid Transmission Word Detected state

When the procedure is in the Second Invalid Transmission Word Detected state, checking for an invalid Transmission Word shall be performed. Any invalid Transmission Word shall cause the Second Invalid Transmission Word Detected state to transition to the Third Invalid Transmission Word Detected state (transition 3). If two consecutive Transmission Words that are not Invalid Transmission Words are received, the Second Invalid Transmission Word Detected state (transition 5). A Loss-of-Signal condition shall cause the Second Invalid Transmission Word Detected state to transition to the Loss of Synchronization state (transition 4). A reset condition imposed upon the receiver shall cause the Second Invalid Transmission Word Detected state to transition to the Reset state (transition 6).

### 6.3.5.3.5 Third Invalid Transmission Word Detection state

When the procedure is in the Third Invalid Transmission Word Detected state, checking for an invalid Transmission Word shall be performed. Any invalid Transmission Word shall cause the Third Invalid Transmission Word Detected state to transition to the Loss of Synchronization state (transition 3). If two consecutive Transmission Words that are not Invalid Transmission Words are received, the Third Invalid Transmission Word Detected state shall transition to the Second Invalid Transmission Word Detected state (transition 5). A Loss-of-Signal condition shall cause the Third Invalid Transmission Word Detected state to transition to the Loss of Synchronization word Detected state to transition to the Loss of Synchronization state (transition 4). A reset condition imposed upon the receiver shall cause the Third Invalid Transmission to the Reset state (transition 6).

#### 6.3.5.4 Reset state

I

When a receiver reset condition is imposed on a receiver, either internally or externally, the receiver shall enter the Reset state (transition 6). Once the Reset state is entered, the receiver shall become not operational and shall remain in the Reset state until it is subsequently made operational by exiting the receiver reset condition.

NOTE 11 - A typical use of receiver reset is to force a receiver in the Loss of Synchronization State to attempt reacquisition of Bit Synchronization. Entry into this state does not necessarily indicate loss of Bit Synchronization.

When the receiver is operational after exiting from a receiver reset condition imposed upon it, either externally or internally, the receiver shall enter the Loss of Synchronization state.

NOTE 12 - The conditions required for a receiver in the Reset state to exit that state are not defined by this standard. Such conditions may be based on explicit indications. They may also be time-dependent in nature.

# 6.4 64B/66B Transmission Word Synchronization

### 6.4.1 Overview

I

64B/66B Transmission Word Synchronization state shall be maintained as specified by the Lock state machine and the BER monitor state machine of the Physical Coding Sublayer (PCS) for 64B/66B, type 10GBASE-R (see subclause 49.2.13 of IEEE 802.3-2012):

- a) if the block\_lock flag of the Lock state machine is TRUE, the hi\_ber flag of the BER monitor state machine is FALSE, and the receiver is not indicating Loss-of-Signal, the receiver Transmission Word Synchronization state shall be Word Synchronization Acquired; and

- b) if the block\_lock flag of the Lock state machine is FALSE, the hi\_ber flag of the BER monitor state machine is TRUE, or the receiver is indicating Loss-of-Signal, the receiver Transmission Word Synchronization state shall be Loss of Synchronization.

If a receiver is decoding 64B/66B that has been further encoded with FEC (see 5.3.1 and 9.3.7.2.1), loss of FEC block synchronization (see subclause 74.10 of IEEE 802.3-2012) is indicated by the value of the fec\_signal\_ok variable of the FEC block synchronization state machine. A value of FALSE for the fec\_signal\_ok variable of the FEC block synchronization state machine shall be treated as a Loss-of-Signal indication by the receiver.

The Lock state machine relies on the property of the 64B/66B Transmission code that a bit value transition is always encoded between the two least significant bits of a Transmission Word, and because of scrambling is unlikely to occur consistently at any other 66-bit period in the encoded bit stream.

Other than loss of Bit Synchronization, signal conditions (e.g., code violation detection) detected between expected synchronization headers do not affect the receiver Transmission Word Synchronization state during use of the 64B/66B transmission code.

#### 6.4.2 64B/66B Transmission Word Synchronization for speed negotiation

If the link speed negotiation algorithm (see 8.6) is performed using 64B/66B, then the pass sync\_test count shall be 1 000.

# 6.4.3 Detection of an invalid 64B/66B Transmission Word

An invalid 64B/66B Transmission Word shall be recognized by the receiver:

- a) if both bits in the Synchronization Header have the same value, then the Transmission Word shall cause a code violation (i.e., Invalid Synchronization Header, see 5.3.4) to be reported;

- b) if a Transmission Word type is decoded that is restricted in table 10, then the Transmission Word shall cause a code violation (i.e., Restricted Transmission Word type, see 5.3.6) to be reported;

- c) if a control code value other than Idle or LPI (i.e., if the FC\_Port supports Energy Efficient Fibre Channel), is decoded, then the Transmission Word shall cause a code violation (i.e., Restricted Control Code, see 5.3.6) to be reported;

- d) if a restricted order code value is decoded, the Special Function shall cause a code violation (i.e., Restricted Order Code, see 5.3.6) to be reported;

- e) an Idle followed by SOF Transmission Word shall cause a code violation (i.e., Idle followed by SOF error, see 5.3.6.2) to be reported if the Transmission Word received prior to receiving an Idle followed by SOF Transmission Word:

- A) was a data Transmission Word;

- B) was any Transmission Word containing an SOF; or

- C) caused a coding violation to be reported;

- f) an EOF followed by Idle or LPI Transmission Word shall cause a code violation (i.e., EOF followed by Idle or LPI error, see 5.3.6.3) to be reported if the Transmission Word received following receiving an EOF followed by Idle or LPI Transmission Word:

- A) is a data Transmission Word;

I

- B) is any Transmission Word containing an EOF; or

- C) causes a coding violation to be reported;

- g) an Other Special Function/SOF Transmission Word shall cause a code violation (i.e., Other Special Function / SOF error, see 5.3.6.7) to be reported if the Transmission Word received prior to receiving an Other Special Function/SOF Transmission Word:

- A) was a data Transmission Word;

- B) was any Transmission Word containing an SOF; or

- C) caused a coding violation to be reported;

- h) a SOF/data Transmission Word shall cause a code violation (i.e., SOF/data error, see 5.3.6.8) to be reported if the Transmission Word received prior to receiving an SOF/data Transmission Word:

- A) was a data Transmission Word;

- B) was any Transmission Word containing an SOF; or

- C) caused a coding violation to be reported;

- i) a data/EOF Transmission Word shall cause a code violation (i.e., data/EOF error, see 5.3.6.9) if the Transmission Word received following receiving a data/EOF Transmission Word: