# 64GFC PCS/FEC Architecture Proposal for FC-FS-5

T11-2016-314v7

Adrian Butter

#### Supporters

- Scott Kipp (Brocade)

- Anil Mehta (Brocade)

- Jeff Slavick (Broadcom Ltd)

- Raul Oteyza (Cavium, Inc)

- Dean Wallace (Cavium, Inc)

#### Introduction

- Over the last year, IEEE has taken steps towards 50G single-lane, 100G dual-lane and 200G quad-lane standardization

- First "Flash mob" in May 2015

- CFI in Nov 2015

- First Study Group meeting in Jan 2016

- First Task Force (P802.3cd) meeting in May 2016

- P802.3cd is currently establishing technical baselines for a 50/100/200G standard

- Complete set of technical baselines scheduled to be available in Sept 2016

- P802.3cd Task Force approved PCS/FEC technical baseline at July 2016 meeting

- The intent of this presentation is two-fold:

- Propose an architecture for 64GFC based on the existing 32GFC and 128GFC standards, with updates reflecting the PCS/FEC technical baseline adopted by P802.3cd

- Highlight the differences between the 64GFC PCS/FEC and 32GFC PCS/FEC as documented in FC-FS-4

- Updated slides from 16-314v6 denoted by

- Remove 10-Bit Symbol Distribution & Bit Multiplexing operations:

- Ethernet use case (50GAUI-2 / LAUI-2 extension interface) not applicable to Fibre Channel

- Removal does not negatively effect clock content or baseline wander (see T11-2017-00094-v1)

- Buys back about 0.5 dB margin...

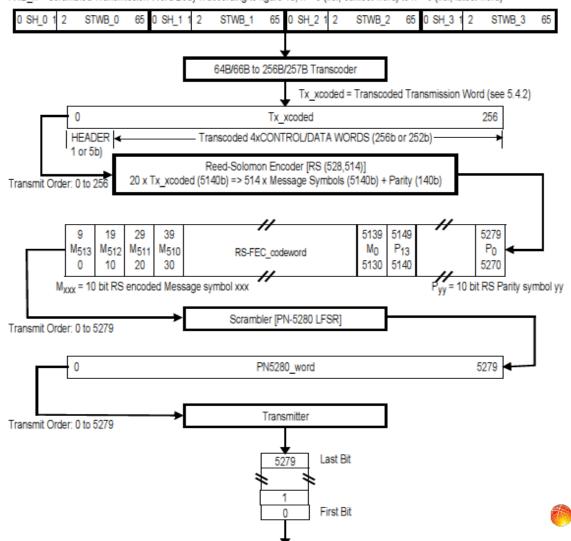

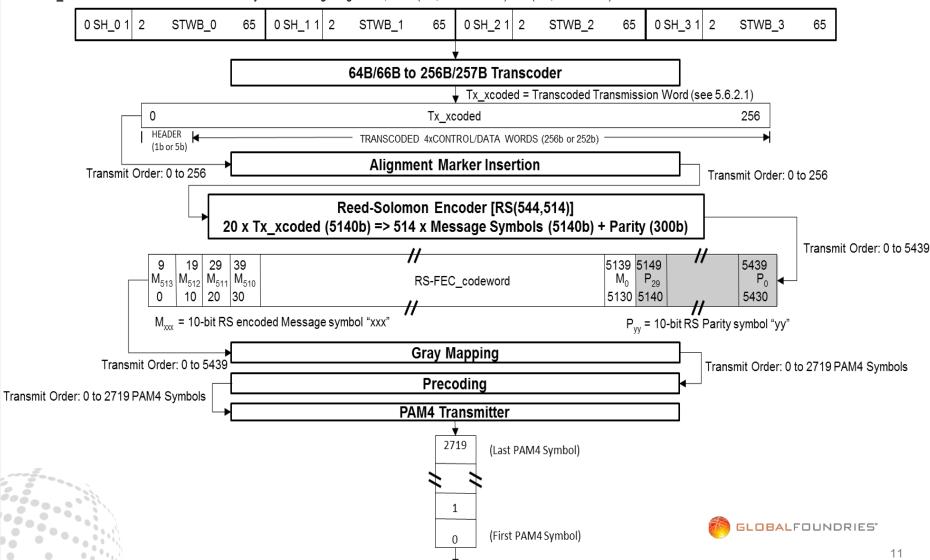

#### 32GFC Architecture – Tx Processing

FC-FS-4 Figure 28:

SH\_n = Synchronization Header n according to figure 10 TWB\_n = Scrambled Transmission Word Body n according to figure 10; n = 0 (i.e., earliest word) to n = 3 (i.e., latest word)

**GLOBALFOUNDRIES**°

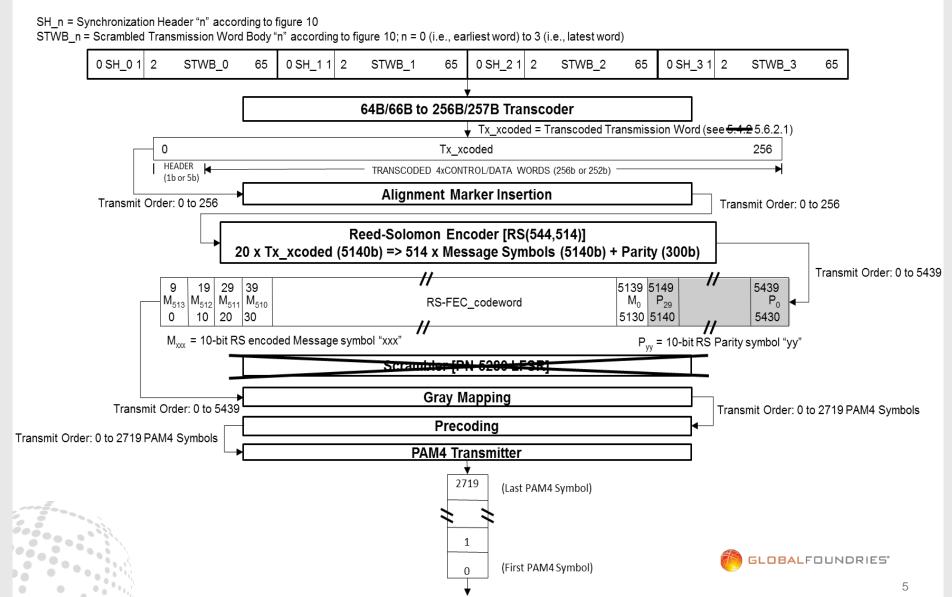

#### Proposed 64GFC Architecture – Tx Processing

#### Proposed 64GFC Architecture – Tx Processing

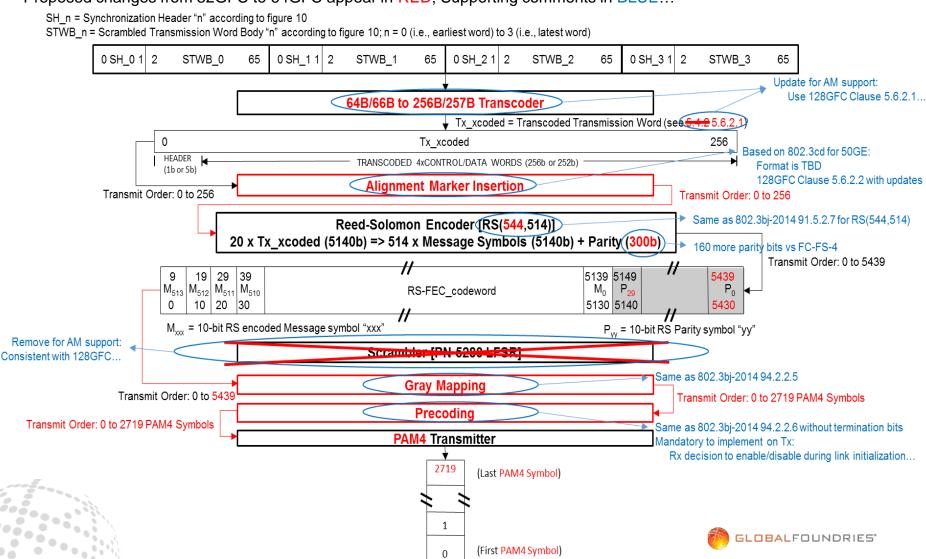

Proposed changes from 32GFC to 64GFC appear in RED; Supporting comments in BLUE...

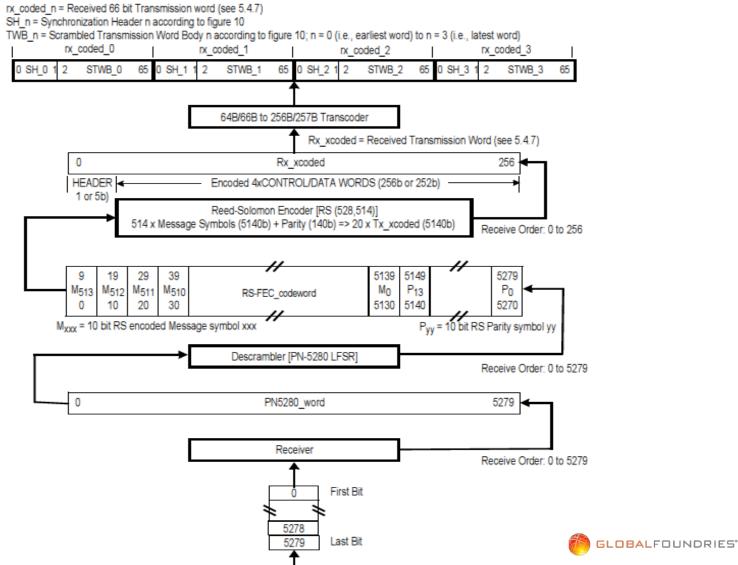

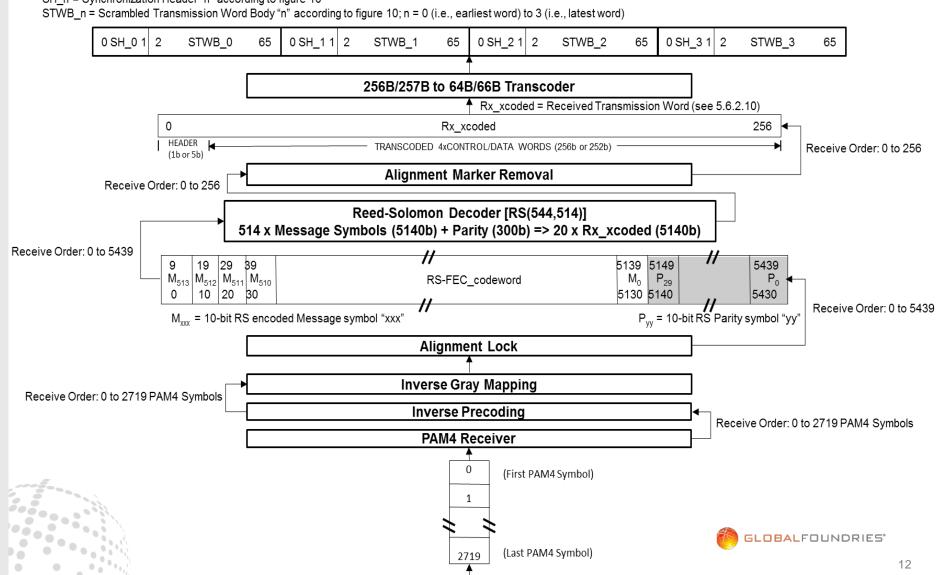

#### 32GFC Architecture – Rx Processing

FC-FS-4 Figure 29:

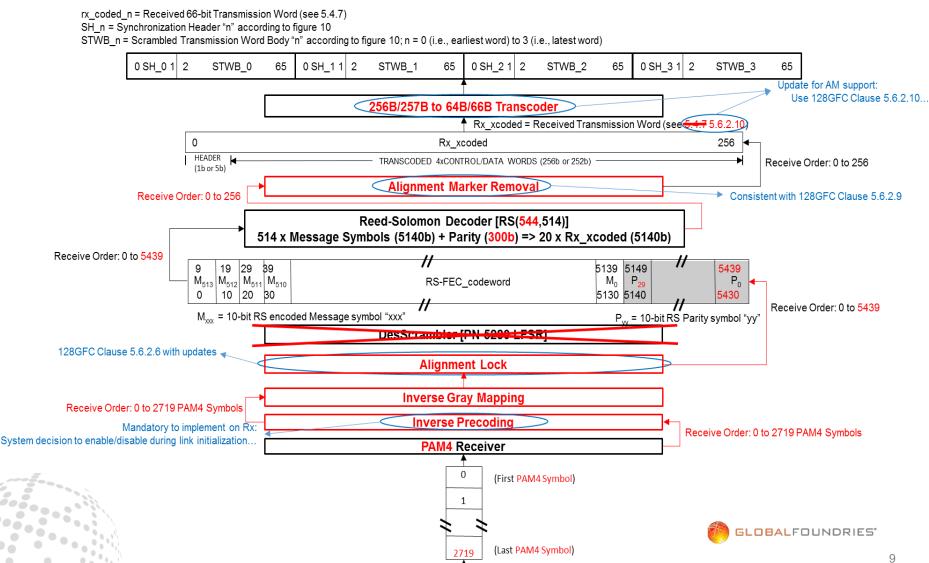

#### Proposed 64GFC Architecture – Rx Processing

rx coded n = Received 66-bit Transmission Word (see 5.4.7) SH n = Synchronization Header "n" according to figure 10 STWB\_n = Scrambled Transmission Word Body "n" according to figure 10; n = 0 (i.e., earliest word) to 3 (i.e., latest word) 0 SH 0 1 2 0 SH 11 STWB 0 65 STWB 1 0 SH 21 2 STWB 2 65 0 SH 3 1 2 STWB 3 65 256B/257B to 64B/66B Transcoder Rx xcoded = Received Transmission Word (see 5.4.7 5.6.2.10) Rx xcoded 256 HEADER TRANSCODED 4xCONTROL/DATA WORDS (256b or 252b) Receive Order: 0 to 256 (1b or 5b) **Alignment Marker Removal** Receive Order: 0 to 256 Reed-Solomon Decoder [RS(544,514)] 514 x Message Symbols (5140b) + Parity (300b) => 20 x Rx\_xcoded (5140b) Receive Order: 0 to 5439 29 39 5139 5149 19 5439  $M_{512} M_{511} M_{510}$ P<sub>29</sub> RS-FEC codeword 20 5130 5140 5430 Receive Order: 0 to 5439 P<sub>yy</sub> = 10-bit RS Parity symbol "yy" M<sub>xxx</sub> = 10-bit RS encoded Message symbol "xxx" **Alignment Lock Inverse Gray Mapping** Receive Order: 0 to 2719 PAM4 Symbols Inverse Precoding Receive Order: 0 to 2719 PAM4 Symbols PAM4 Receiver (First PAM4 Symbol) **GLOBALFOUNDRIES**°

2719

(Last PAM4 Symbol)

#### Proposed 64GFC Architecture – Rx Processing

Proposed changes from 32GFC to 64GFC appear in RED; Supporting comments in BLUE...

### 32GFC to 64GFC Update Summary

| 64GFC Update                                  | Rationale Changes from 32GFC                                                                                                                                                                                                                               |                                                                                                                                                                                                                 |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0401 C Opdate                                 | Nationale                                                                                                                                                                                                                                                  | Changes Hom 3201 C                                                                                                                                                                                              |

| Include Alignment Marker                      | 1) Improves Rx lock time: For 25GE, 300 usec vs 500 usec => 1.7x reduction 2) Commonality with 50GE (P802.3cd) 3) Supports reuse of 802.3 work                                                                                                             | <ol> <li>Add Tx AM Insertion</li> <li>Add Rx Alignment Lock</li> <li>Add Rx AM Removal</li> <li>Remove Tx Scrambler &amp; Rx Descrambler</li> <li>Update Tx &amp; Rx 64B/66B to 256B/257B Transcoder</li> </ol> |

| Include Stronger FEC                          | Current 32GFC RS(528,514) FEC is insufficient to meet the FC-PI-7 BER objective                                                                                                                                                                            | 1) Replace RS(528,514) coder with RS(544,514) coder                                                                                                                                                             |

| Include Bit Multiplexing of 10-Bit<br>Symbols | Aligns with 50GE (P802.3cd)     Supports reuse of P802.3cd baseline wander & clock content analyses                                                                                                                                                        | <ol> <li>Add Tx 10-bit Symbol Distribution &amp;<br/>Rx 10-bit Symbol Multiplexing</li> <li>Add Tx Bit Multiplexing &amp; Rx Bit<br/>Distribution</li> </ol>                                                    |

| Include PAM-4 Signaling                       | Aligns with 400GE (P802.3bs) & adopted as the technical baseline for 50GE (P802.3cd)                                                                                                                                                                       | <ol> <li>Add Tx Gray Mapping</li> <li>Add Rx Inverse Gray Mapping</li> </ol>                                                                                                                                    |

| Include Precoding                             | <ol> <li>Improves performance of links susceptible to burst errors caused by large DFE tap weights</li> <li>Low complexity to implement: Estimated at &lt;500 logic gates</li> <li>Adopted as an implementation requirement for 50GE (P802.3cd)</li> </ol> | Add Tx Precoding     Add Rx Inverse Precoding                                                                                                                                                                   |

#### 64GFC Transmit Bit Ordering Diagram

SH\_n = Synchronization Header "n" according to figure 10

STWB\_n = Scrambled Transmission Word Body "n" according to figure 10; n = 0 (i.e., earliest word) to 3 (i.e., latest word)

#### 64GFC Receive Bit Ordering Diagram

rx\_coded\_n = Received 66-bit Transmission Word (see 5.4.7)

SH n = Synchronization Header "n" according to figure 10

## Thank you!