# FC-FS-4 modifications for incorporating 256B/257B transcoding

T11/13-115v0

#### Bill Martin

#### wrmartin@surewest.net

## A Issue

The following modifications are necessary in FC-FS-4 to accommodate 66B/67B transcoding for 32GFC.

## 2.3 References under development

Editors Note 1 - WRM: add the following reference under development

**IEEE 802.3bj-201X**: IEEE 802.3bj-201X, Draft Standard for Ethernet Amendment X: Physical Layer Specifications and Management Parameters for 100 Gb/s Operation Over Backplanes and Copper Cables

Editors Note 2 - WRM: Add new subclause 5.4

## 5.4 256B/257B transmission code

### 5.4.1 Overvie

An FC-0 standard (e.g., FC-PI-6) may specify the use of the 256B/257B transmission code as its frame transfer transmission code. If the 256B/257B transmission code is specified, it shall be:

- a) generated as described in 5.4.2;

- b) encoded with Reed Solomon coding as described in 5.4.3;

- c) scrambled as described in 5.4.4

- d) descrambled as described in 5.4.5

- e) decode with the Reed Solomon decoder as described in 5.4.6; and

- f) decoded as described in 5.4.7.

## 5.4.2 64B/66B to 256B/257B Transcoding

The 256B/257B transmission code specified by this standard operates on 4 consecutive 64B/66B Transmission Words, each group being encoded as a 257-bit Transmission Word.

NOTE 1 - The IEEE 802.3bj-201X specification of 256B/257B references as "blocks" what this standard references as "Transmission Words".

The transcoder constructs a 257-bit block from a group of 4 x 66-bit Transmission Words to allocate bandwidth for the parity check symbols added by the Reed-Solomon encoder.

The 257-bit block  $tx_xcoded<256:0>$  shall be constructed as defined in IEEE 802.3bj-201X 91.5.2.5 given 4 x 66-bit Transmission Words denoted as  $tx_coded_j<65:0>$  where j=0 to 3. The first 5 bits of  $tx_xcoded<256:0>$  are not scrambled, i.e. the step that generates  $tx_scrambled<256:0>$  is not performed.

A stream of 256B/257B Transmission Words on a link may be further encoded to provide Forward Error Correction (i.e., FEC). The use of FEC is negotiated during transmitter training (see clause 9). How an FC\_Port determines to request use of FEC is not within the scope of this standard. An FC\_Port that does not perform transmitter training shall not use FEC.

If the FC\_Ports on a link determine to use FEC, the streams of 256B/257B Transmission Words in both directions on the link shall be encoded as specified in 5.4 and then further encoded as specified in subclause 74.7 and subclause 74.10 of IEEE 802.3-2008. If the FC\_Ports on a link determine not to use FEC, the streams of 64B/66B Transmission Words in both directions on the link shall be encoded as specified in 5.3.

### 5.4.3 Reed-Solomon encoder

The RS-FEC sublayer employs a Reed-Solomon code operating over the Galois Field GF(2<sup>10</sup>) where the symbol size is 10 bits. The encoder processes k message symbols to generate 2t parity symbols which are then appended to the message to produce a codeword of n=k+2t symbols. For the purposes of this clause, a particular Reed-Solomon code is denoted RS(n, k).

When used to form a 100GBASE-CR4 or 100GBASE-KR4 PHY, the RS-FEC sublayer shall implement RS(528, 514). When used to form a 100GBASE-KP4 PHY, the RS-FEC sublayer shall implement RS(544, 514). Each k-symbol message corresponds to twenty 257-bit blocks produced by the transcoder. Each code is based on the generating polynomial given by Equation (91–1).

### 5.4.4 Scrambler

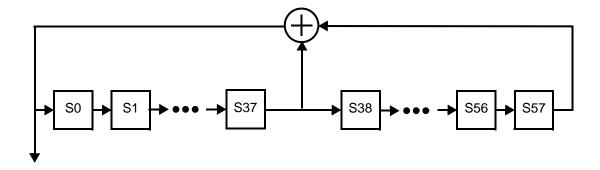

Each RS-FEC codeword is scrambled with a known sequence to randomize the 257-bit block headers and to enable robust codeword synchronization at the receiver (it ensures that any shifted input bit sequence is not equal to another RSFEC codeword). Scrambling is implemented as modulo-2 addition of the RS-FEC codeword and a pseudo-noise sequence 5280 bits in length (PN-5280) (see figure 1).

PN-5280 is generated by the polynomial r(x).

$$r(x) = S^{39} + S^{58} + 1$$

Figure 1 - PN-5280 as a linear feedback shift register

At the start of each RS-FEC codeword, the initial state of the pseudo-noise generator is set to S57 = 1,  $Si-1 = Si \times Si$  XOR 1 or, in other words, a binary sequence of alternating 1's and 0's.

### 5.4.5 Descrambler

Each codeword shall be descrambled prior to decoding. Descrambling is implemented as the modulo-2 addition of RS-FEC codeword and the same pseudonoise sequence (PN-5280) defined for the scrambler (see 5.4.4).

## 5.4.6 Reed-Solomon decoder

The Reed-Solomon decoder extracts the message symbols from the codeword, correcting them as necessary, and discards the parity symbols. The message symbols correspond to 20 x 257-bit blocks.

The Reed-Solomon decoder shall be capable of correcting any combination of up to t=7 symbol errors in a codeword. It shall also be capable of indicating when a codeword contains errors but was not corrected, e.g. it contains a number of errors in excess of the error correction capability.

### 5.4.7 256B/257B to 64B/66B transcoder

The transcoder extracts a group of 4 x 66-bit Transmission Words from each received 257-bit Transmission Word.

The 4 x 66-bit Transmission Words, denoted as rx\_coded\_j<65:0> where j=0 to 3, shall be derived from each 257-bit block rx\_xcoded<256:0> as defined in IEEE 802.3bj-201X 91.5.2.5. As the first 5 bits of rx\_xcoded<256:0> are not scrambled, the step that derives rx\_xcoded from rx\_scrambled is not performed.