#### INCITS working draft proposed American National Standard for Information Technology

#### T11/15-253v2

Secretariat: Information Technology Industry Council

NOTE: This is a working draft American National Standard of Accredited Standards Committee INCITS. As such this is not a completed standard. The T11 Technical Committee may modify this document as a result of comments received anytime, or during a future public review and its eventual approval as a Standard. Use of the information contained herein is at your own risk.

Permission is granted to members of INCITS, its technical committees, and their associated task groups to reproduce this document for the purposes of INCITS standardization activities without further permission, provided this notice is included. All other rights are reserved. Any duplication of this document for commercial or for-profit use is strictly prohibited.

#### POINTS OF CONTACT:

I

| Steven L. Wilson (T11 Chair)   | Claudio DeSanti (T11 Vice Chair) |                                      |

|--------------------------------|----------------------------------|--------------------------------------|

| Brocade                        | Cisco Systems                    |                                      |

| 1745 Technology Drive          | 170 W. Tasman Drive              |                                      |

| San Jose, CA 95131             | San Jose, CA 95134               |                                      |

| Voice: 408-333-8128            | Voice: 408-853-9172              |                                      |

| swilson@brocade.com            | cds@cisco.com                    |                                      |

| Craig W. Carlson (T11.3 Chair) | David Peterson (FC-FS-4 Chair)   | Craig W. Carlson (FC-FS-4<br>Editor) |

| QLogic Corporation             | Brocade                          | QLogic Corporation                   |

| 12701 Whitewater Drive         | 6000 Nathan Lane North           | 12701 Whitewater Drive               |

| Minnetonka, MN 55343           | Plymouth, MN 55442               | Minnetonka, MN 55343                 |

| Voice: 952-687-2431            | Voice: 612-802-3299              | Voice: 952-687-2431                  |

| craig.carlson@qlogic.com       | david.peterson@brocade.com       | craig.carlson@qlogic.com             |

|                                |                                  |                                      |

# **Revision History**

# Rev 1.40 - 7 October 2015

a) Incorporates T11 Letter Ballot comment resolutions (see T11/15-054v6).

# Rev 1.30 - 7 September 2015

a) Incorporates T11 Letter Ballot comment resolutions (see T11/15-054v5).

# Rev 1.20 - 21 July 2015

a) First draft incorporating T11 Letter Ballot comment resolutions (see T11/15-054v4).

## Rev 1.10 - 5 August 2014

a) Changes discussed during 8/5/14 FC-FS-4 working group meeting.

## Rev 1.00 - 21 July 2014

- a) Incorporated T11/14-192v1.

- b) Fixed incorporation errors with 10-430v1.

- c) Incorporated T11/14-196v0.

- d) Incorporated T11/14-219v0.

# Rev 0.50 - 16 May 2014

- a) Incorporated T11/13-445v0 except for last two comments

- b) Incorporated T11/14-003v1.

- c) Incorporated T11/14-097v1.

- d) Incorporated approved comments from 14-058v2. See 14-058v3 for remaining open comments.

# Rev 0.40 - 29 January 2014

a) Incorporated T11/13-369v1 "128GFC Architecture Text" (approved by work group on 4 December 2013)

## Rev 0.30 - 29 October 2013

- a) Incorporated T11/13-115v4 "FC-FS-4 modifications for incorporating 256B/257B transcoding" (approved by work group on 7 October 2013)

- b) Cleaned up change tracking markups from previous revisions.

# Rev 0.20 - 14 March 2013

a) Incorporated T11/13-011v1 "Energy Efficient Flbre Channel" (approved by work group on 4 February 2013)

# Rev 0.10 - 17 April 2012

- a) Based on ANSI INCITS 470-2011 FC-FS-3 revision 1.11

- b) Incorporated T11/11-206v1 "CS\_CTL and Proirity clarifications for FC-FS-4" (approved by work group on 6 June 2011)

- c) Incorporated T11/10-430v1 "Changes for Sequence ID uniqueness" (approved by work group on 1 August 2011)

- d) Incorporated T11/11-385v2 "ABTS enhancement text" (approved by work group on 5 December 2011)

- e) Incorporated T11/11-511v0 "SB-5 Abort Codes" (approved by work group on 5 December 2011)

- f) Incorporated T11/12-106v0 with Option 2 "Corrections to FC-FS-4 for Dr. Alexandrov" (approved by work group 16 April 2012)

- g) Incorporated T11/12-047v1 "Corrections to FC-FS-4 for T11/10-427" (approved by work group 16 April 2012)

- h) Removed double spaces throughout document

draft proposed American National Standard for Information Technology

Fibre Channel – Fibre Channel Framing and Signaling - 4 (FC-FS-4)

Secretariat

Information Technology Industry Council

Approved dd mmmmm, 200x

American National Standards Institute, Inc.

#### Abstract

This standard describes the framing and signaling requirements for Fibre Channel links. The Physical Interface requirements are described in Fibre Channel-Physical Interfaces (FC-PI-x). The Link Services requirements are described in Fibre Channel-Link Services (FC-LS-3). This standard is recommended for new implementations but does not obsolete the existing Fibre Channel standards.

#### **American National Standard**

Approval of an American National Standard requires review by ANSI that the requirements for due process, consensus, and other criteria for approval have been met by the standards developer.

Consensus is established when, in the judgement of the ANSI Board of Standards Review, substantial agreement has been reached by directly and materially affected interests. Substantial agreement means much more than a simple majority, but not necessarily unanimity. Consensus requires that all views and objections be considered, and that a concerted effort be made towards their resolution.

The use of American National Standards is completely voluntary; their existence does not in any respect preclude anyone, whether he has approved the standards or not, from manufacturing, marketing, purchasing, or using products, processes, or procedures not conforming to the standards.

The American National Standards Institute does not develop standards and will in no circumstances give an interpretation of any American National Standard. Moreover, no person shall have the right or authority to issue an interpretation of an American National Standard in the name of the American National Standards Institute. Requests for interpretations should be addressed to the secretariat or sponsor whose name appears on the title page of this standard.

**CAUTION NOTICE:** This American National Standard may be revised or withdrawn at any time. The procedures of the American National Standards Institute require that action be taken periodically to reaffirm, revise, or withdraw this standard. Purchasers of American National Standards may receive current information on all standards by calling or writing the American National Standards Institute.

#### PATENT STATEMENT

The developers of this standard have requested that holders of patents that may be required for the implementation of the standard disclose such patents to the publisher. However, neither the developers nor the publisher have undertaken a patent search in order to identify which, if any, patents may apply to this standard. As of the date of publication of this standard, following calls for the identification of patents that may be required for the implementation of the standard, notice of one or more such claims has been received. By publication of this standard, no position is taken with respect to the validity of this claim or of any rights in connection therewith. The known patent holder(s) has (have), however, filed a statement of willingness to grant a license under these rights on reasonable and nondiscriminatory terms and conditions to applicants desiring to obtain such a license. Details may be obtained from the publisher. No further patent search is conducted by the developer or publisher in respect to any standard it processes. No representation is made or implied that this is the only license that may be required to avoid infringement in the use of this standard.

Published by

#### American National Standards Institute, Inc. 11 West 42nd Street, New York, NY 10036

Copyright  $\ensuremath{\mathbb{C}}$  2012 by Information Technology Industry Council (ITI) All rights reserved.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without prior written permission of ITI, 1250 Eye Street NW, Washington, DC 20005.

Printed in the United States of America

# **Table of Contents**

| С | Contents Page                                         |     |

|---|-------------------------------------------------------|-----|

|   | Scope                                                 |     |

| 2 | References                                            |     |

|   | 2.1 Qualification and availability of references      | - 2 |

|   | 2.2 Approved references                               | - 2 |

|   | 2.3 References under development                      | - 4 |

|   | 2.4 Other references                                  |     |

| 3 | Definitions, abbreviations, conventions and keywords  | - 6 |

|   | 3.1 Definitions                                       |     |

|   | 3.2 Editorial conventions                             |     |

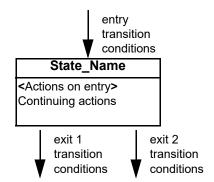

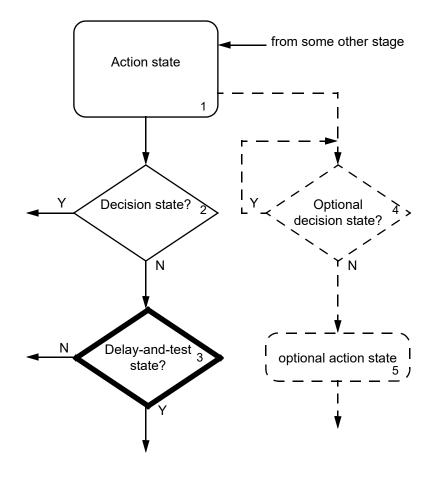

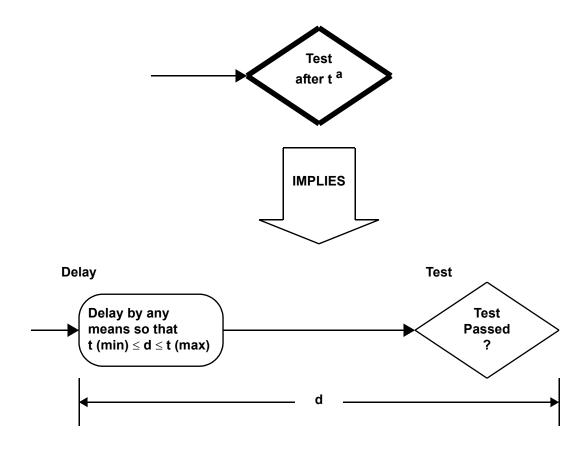

|   | 3.3 State machines                                    |     |

|   | 3.3.1 Overview                                        |     |

|   | 3.3.2 States                                          |     |

|   | 3.3.3 State variables                                 |     |

|   | 3.3.4 State transitions                               |     |

|   | 3.3.5 State diagram conventions                       |     |

|   | 3.4 Abbreviations, acronyms, and symbols              | 19  |

|   | 3.4.1 Acronyms and other abbreviations                |     |

|   | 3.4.2 Symbols                                         |     |

|   | 3.5 Keywords                                          |     |

|   |                                                       |     |

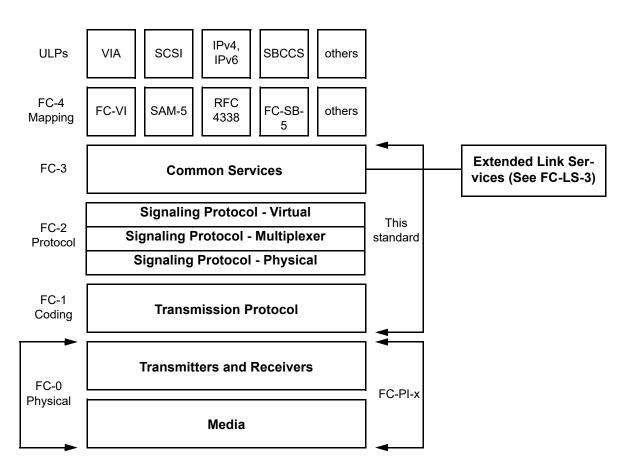

| 4 | Structure and Concepts                                | 25  |

|   | 4.1 Introduction                                      | -   |

|   | 4.2 Functional levels                                 | -   |

|   | 4.2.1 Overview         4.2.2 FC-0 general description |     |

|   | 4.2.2 FC-0 general description                        | 20  |

|   | 4.2.3 FC-1 general description                        | 20  |

|   | 4.2.5 FC-3 general description                        | 27  |

|   | 4.2.6 FC-4 general description                        | 27  |

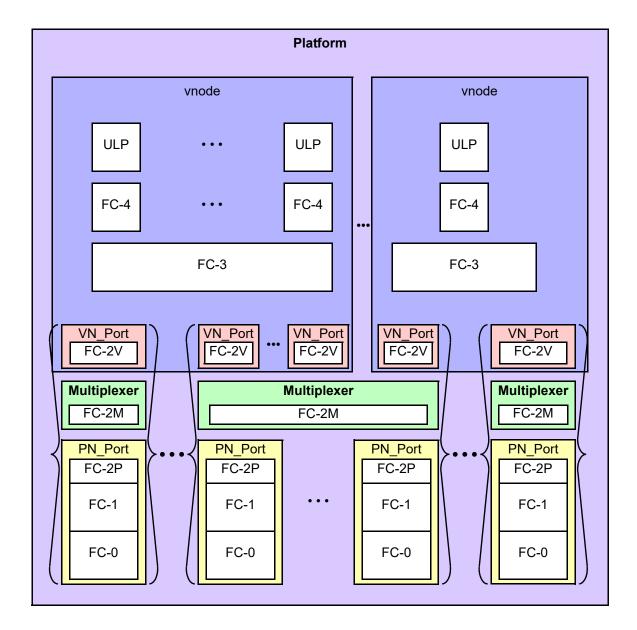

|   | 4.3 Architectural components of nodes                 | 28  |

|   | 4.4 Physical model                                    | 29  |

|   | 4.5 Communication models                              |     |

|   | 4.6 Topology                                          |     |

|   | 4.6.1 Types                                           |     |

|   | 4.6.2 Point-to-point topology                         | 31  |

|   | 4.6.3 Fabric topology                                 | 32  |

|   |                                                       |     |

|   | 4.7 Classes of service                                |     |

|   | 4.7.1 General                                         |     |

|   | 4.7.2 Class 2 service - multiplex                     | 34  |

|   | 4.7.3 Class 3 service - datagram                      |     |

|   | 4.7.4 Class F service - Fabric                        |     |

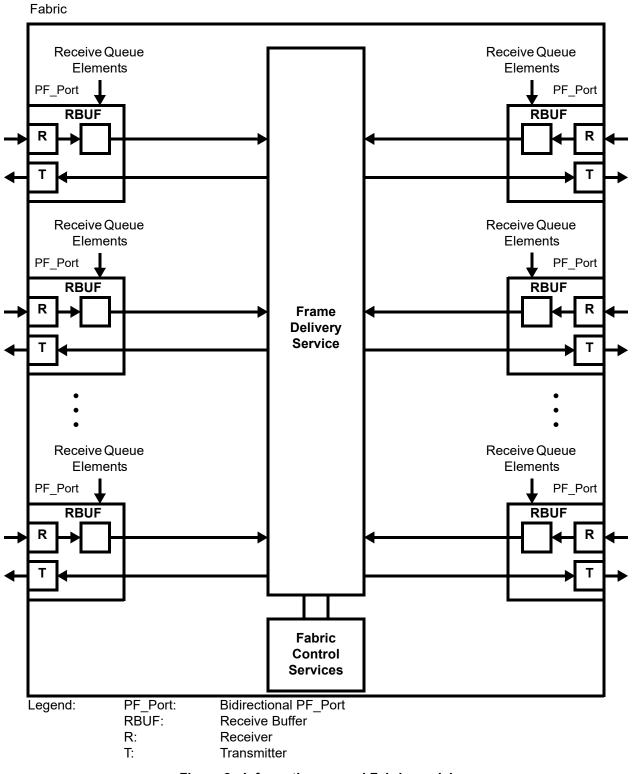

|   | 4.8 General Fabric model                              |     |

|   | 4.8.1 General                                         |     |

|   |                                                       | 37  |

|   | 4.8.3 Frame delivery service                          |     |

|   |                                                       |     |

|   | 4.10 Building Blocks                                  |     |

|   |                                                       | 31  |

|   | 4.10.2 Frame                                            | 38 |

|---|---------------------------------------------------------|----|

|   | 4.10.3 Sequence                                         |    |

|   | 4.10.3.1 Introduction                                   | 39 |

|   | 4.10.3.2 Sequence_Identifier (SEQ_ID)                   | 39 |

|   | 4.10.3.3 Sequence Status Blocks                         | 39 |

|   | 4.10.4 Exchange                                         | 39 |

|   | 4.10.4.1 Introduction                                   | 39 |

|   | 4.10.4.2 Exchange_Identifiers (OX_ID and RX_ID)         | 40 |

|   | 4.10.4.3 Exchange Status Blocks                         | 40 |

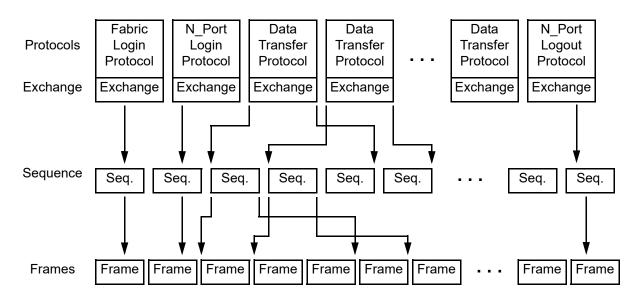

|   | 4.10.5 Protocols                                        | 40 |

|   | 4.10.5.1 Primitive Sequence protocols                   | 40 |

|   | 4.10.5.2 Fabric Login protocol                          | 40 |

|   | 4.10.5.3 Additional N_Port_ID protocol                  | 41 |

|   | 4.10.5.4 N_Port Login protocol                          | 41 |

|   | 4.10.5.5 Data transfer protocol                         | 41 |

|   | 4.10.5.6 Nx_Port Logout protocol                        | 41 |

|   | 4.10.5.7 Fabric Logout protocol                         | 11 |

|   | 4.11 Segmentation and reassembly of application data    | /1 |

|   | 4.12 Error detection and recovery                       | 11 |

|   | •                                                       |    |

| 5 | FC-1 transmission codes                                 | 43 |

|   | 5.1 Overview                                            |    |

|   | 5.2 8B/10B transmission code                            |    |

|   | 5.2.1 Overview                                          |    |

|   | 5.2.2 Notation conventions                              |    |

|   | 5.2.3 Valid 8B/10B Transmission Characters              |    |

|   | 5.2.4 Running disparity                                 | 50 |

|   | 5.2.5 Generating Transmission Characters                | 51 |

|   | 5.2.6 Validity of received Transmission Characters      | 51 |

|   | 5.2.7 8B/10B Ordered Sets                               | 52 |

|   | 5.2.7.1 General                                         |    |

|   | 5.2.7.2 8B/10B Frame delimiters                         | 53 |

|   | 5.2.7.3 8B/10B Primitive Signals                        | 55 |

|   | 5.2.7.4 Idle                                            | 56 |

|   | 5.2.7.5 8B/10B Primitive Sequences                      | 56 |

|   | 5.3 64B/66B transmission code                           | 57 |

|   | 5.3.1 Overview                                          | 57 |

|   | 5.3.2 64B/66B Transmission Word format                  | 57 |

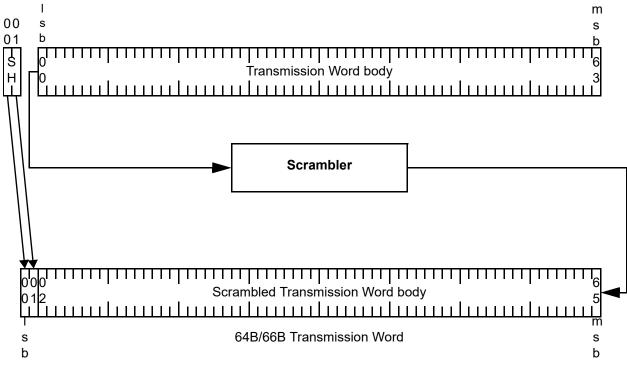

|   | 5.3.3 64B/66B scrambling                                | 58 |

|   | 5.3.4 Invalid Synchronization Header                    | 59 |

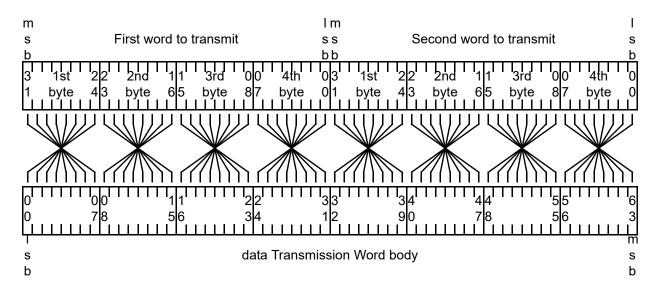

|   | 5.3.5 Data Transmission Words                           | 59 |

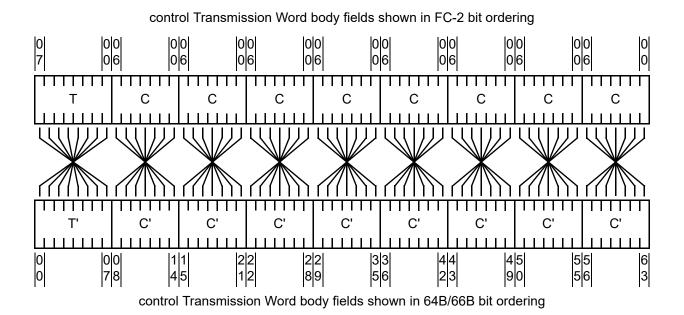

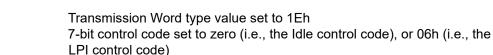

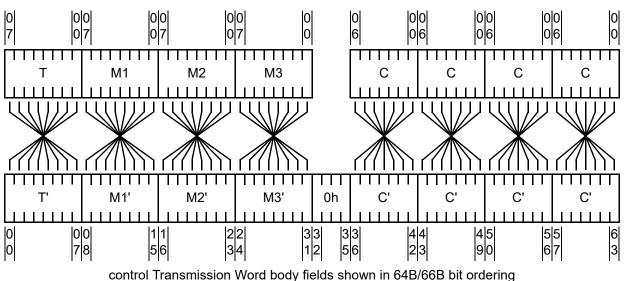

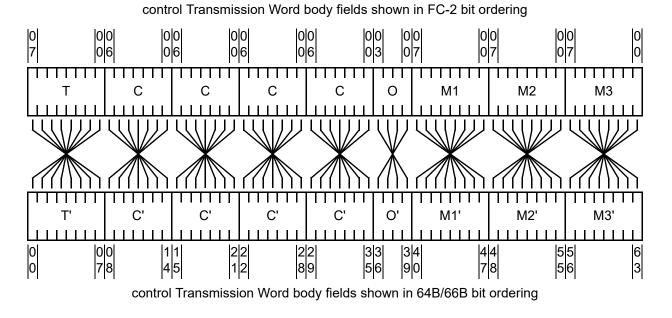

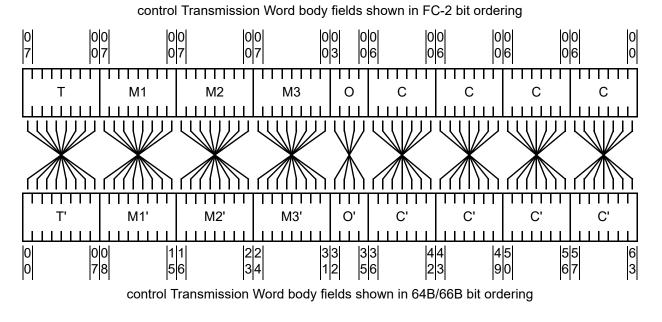

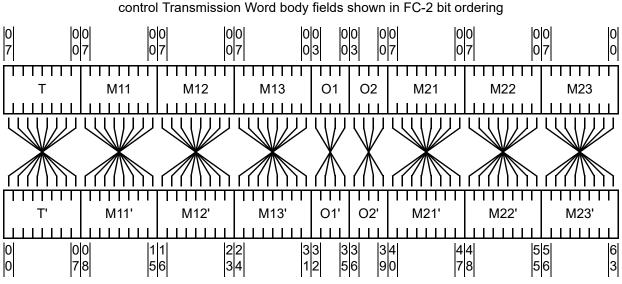

|   | 5.3.6 Control Transmission Words                        |    |

|   | 5.3.6.1 Idle or LPI followed by Idle or LPI             | 62 |

|   | 5.3.6.2 Idle followed by SOF                            | 62 |

|   | 5.3.6.3 EOF followed by Idle or LPI                     | 63 |

|   | 5.3.6.4 Idle / other Special Function                   | 64 |

|   | 5.3.6.5 Other Special Function / Idle                   | 65 |

|   | 5.3.6.6 Other Special Function / other Special Function | 67 |

|   | 5.3.6.7 Other Special Function / SOF                    | 67 |

|   | 5.3.6.8 SOF / data                                      | 68 |

|   | 5.3.6.9 Data / EOF                                      |    |

|   | 5.3.6.10 Receiver error reporting                       |    |

|   | 5.3.7 64B/66B representation of Special Functions       | 71 |

|   | 5.3.7.1 64B/66B frame delimiters                        | 71 |

|   |                                                         | 11 |

|   | 5.3.7.2 64B/66B Primitive Signals                                        | 72 |

|---|--------------------------------------------------------------------------|----|

|   | 5.3.7.3 64B/66B Primitive Sequences                                      | 73 |

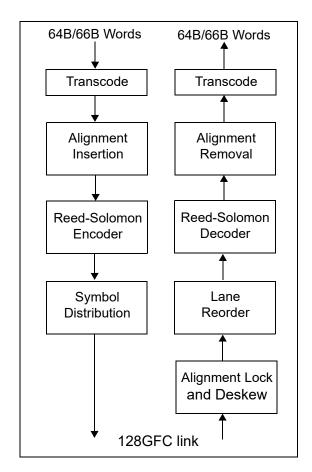

|   | 5.4 256B/257B transmission code                                          | 73 |

|   | 5.4.1 Overview                                                           |    |

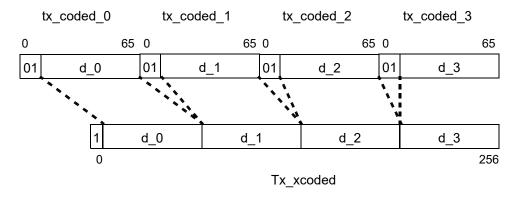

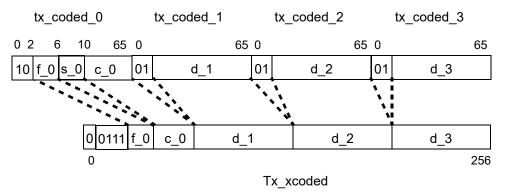

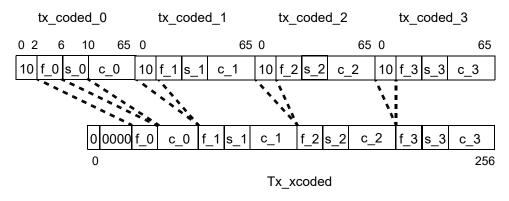

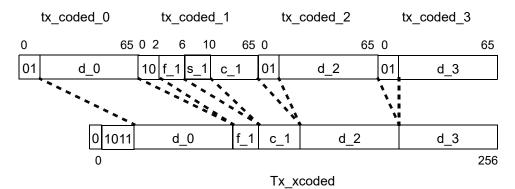

|   | 5.4.2 64B/66B to 256B/257B Transcoding                                   |    |

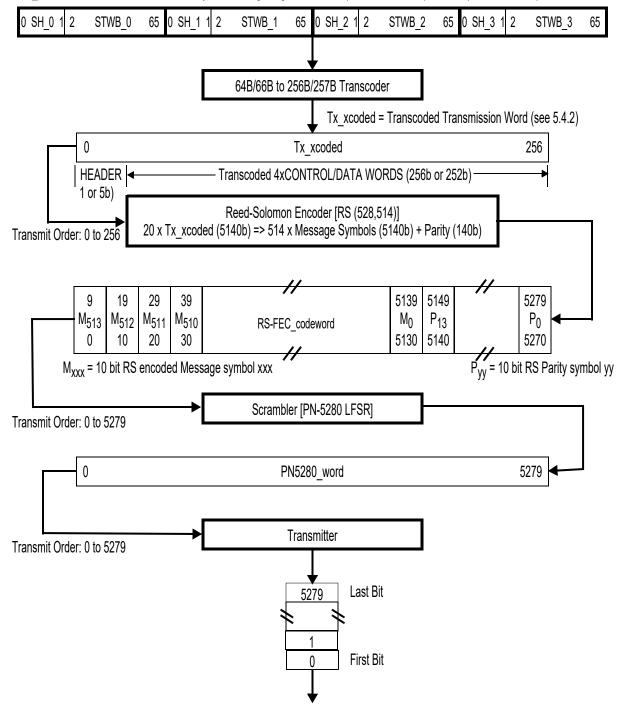

|   | 5.4.3 Reed-Solomon encoder                                               | 77 |

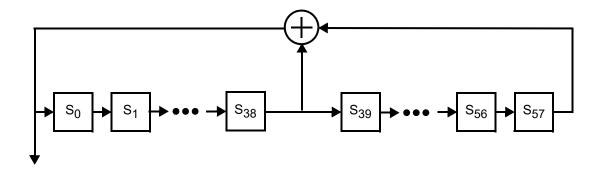

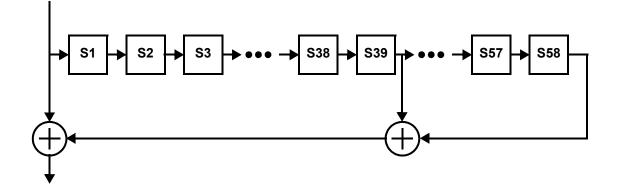

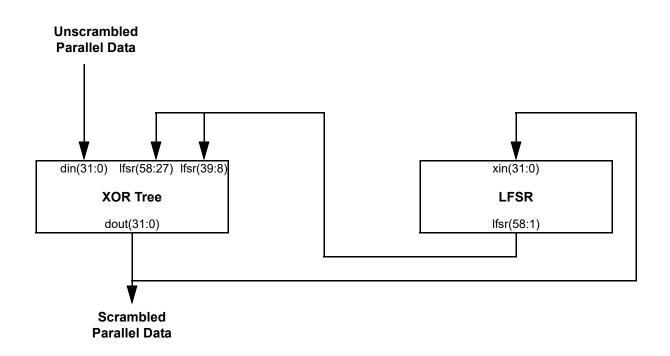

|   | 5.4.4 Scrambler                                                          |    |

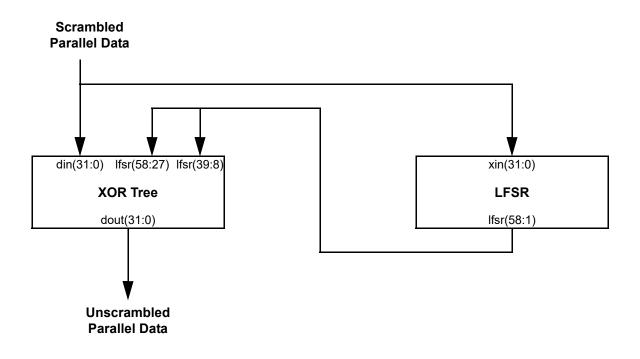

|   | 5.4.5 Descrambler                                                        |    |

|   | 5.4.6 Reed-Solomon decoder                                               |    |

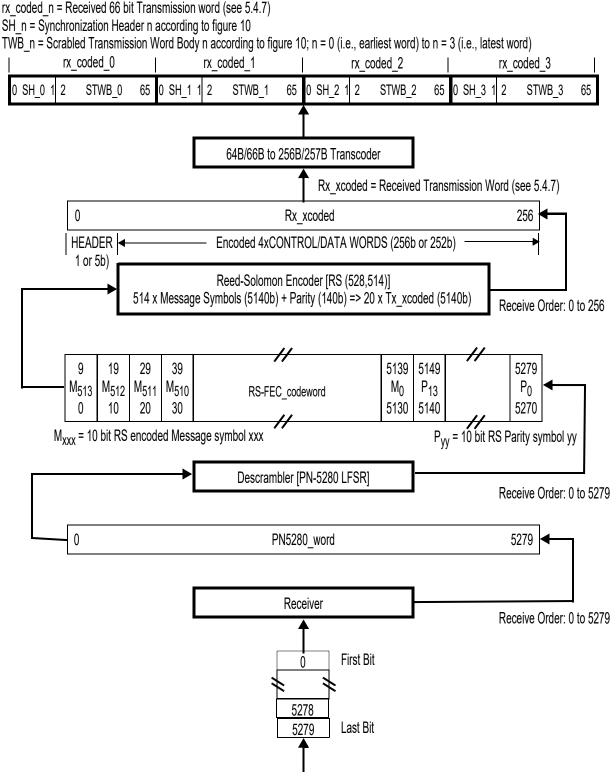

|   |                                                                          |    |

|   | 5.4.7 256B/257B to 64B/66B transcoder                                    | 78 |

|   | 5.4.8 Transmit Bit Ordering                                              | 79 |

|   | 5.4.9 Receive Bit Ordering                                               | 80 |

|   | 5.5 Transmitter Training Signal                                          | 82 |

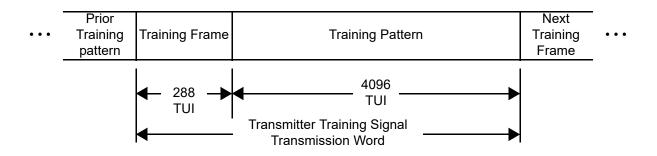

|   | 5.5.1 Overview                                                           |    |

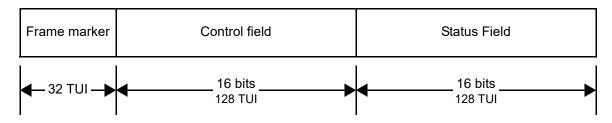

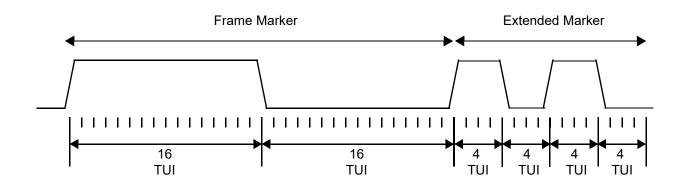

|   | 5.5.2 Training Frame                                                     | 82 |

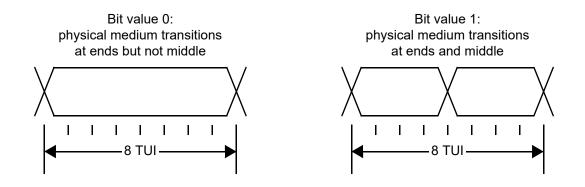

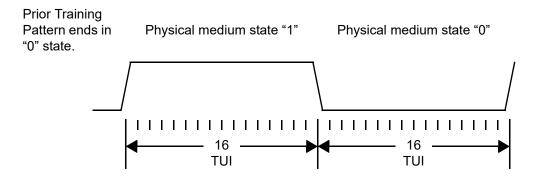

|   | 5.5.3 Training Pattern                                                   | 87 |

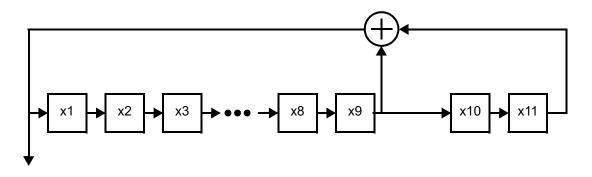

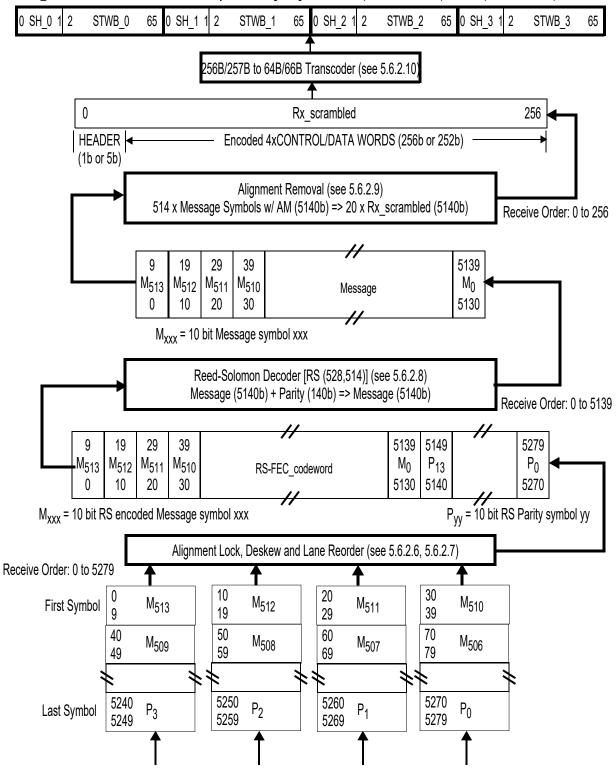

|   | 5.6 FEC for 128GFC                                                       |    |

|   | 5.6.1 Overview                                                           |    |

|   | 5.6.2 Functional block diagram                                           |    |

|   | 5.6.2.1 64B/66B to 256B/257B Transcoder                                  | 00 |

|   | 5.6.2.2 Alignment marker mapping and insertion                           |    |

|   | 5.6.2.3 Reed-Solomon encoder                                             | 09 |

|   | 5.6.2.3 Reed-Solomon encoder                                             | 89 |

|   | 5.6.2.4 Symbol distribution                                              | 89 |

|   | 5.6.2.5 Transmit bit ordering                                            | 89 |

|   | 5.6.2.6 Alignment lock and deskew                                        | 90 |

|   | 5.6.2.7 Lane reorder                                                     |    |

|   | 5.6.2.8 Reed-Solomon decoder                                             | 90 |

|   | 5.6.2.9 Alignment marker removal                                         | 90 |

|   | 5.6.2.10 256B/257B to 64B/66B transcoder                                 | 90 |

|   | 5.6.2.11 Receive bit ordering                                            | 90 |

| - |                                                                          |    |

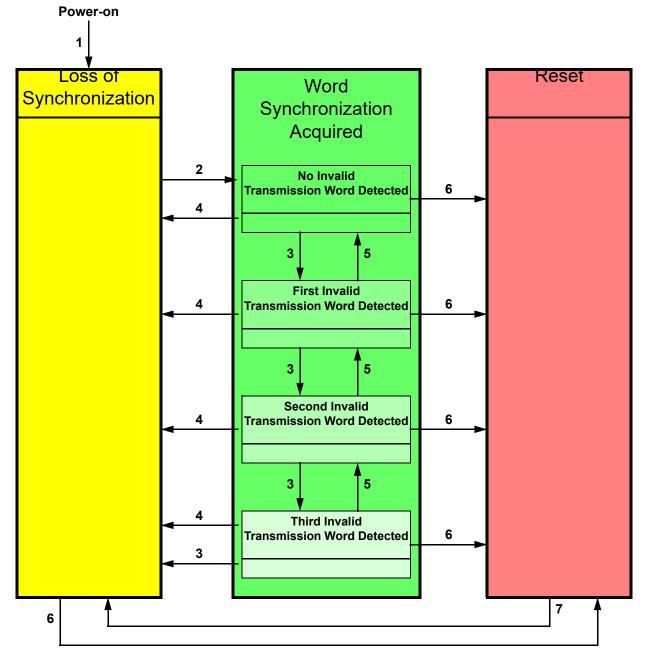

| 6 | FC-1 Transmission Word Synchronization                                   | 93 |

|   | 6.1 Scope                                                                | 93 |

|   | 6.2 Introduction                                                         |    |

|   | 6.3 8B/10B Transmission Word Synchronization                             | 93 |

|   | 6.3.1 State Diagram Overview                                             | 93 |

|   | 6.3.2 Operational and not operational conditions                         | 95 |

|   | 6.3.3 Transmission Word Synchronization Procedure                        | 96 |

|   | 6.3.3.1 Bit Synchronization                                              | 96 |

|   | 6.3.3.2 Transmission Word Synchronization detection                      | 96 |

|   | 6.3.3.2.1 Introduction                                                   | 96 |

|   | 6.3.3.2.2 Achieving Transmission Word Synchronization                    |    |

|   | 6.3.3.2.3 8B/10B Transmission Word Synchronization for speed negotiation | 96 |

|   | 6.3.3.2.4 Transmission Word alignment methods                            | 07 |

|   | 6.3.3.2.4.1 Continuous-mode alignment                                    | 97 |

|   | 6.3.3.2.4.1 Continuous-mode alignment                                    | 97 |

|   | 6.3.3.2.4.2 Explicit-mode alignment                                      | 97 |

|   | 6.3.4 Loss of Transmission Word Synchronization                          | 97 |

|   | 6.3.4.1 Introduction                                                     |    |

|   | 6.3.4.2 Detection of an invalid Transmission Word                        | 97 |

|   | 6.3.5 State transitions                                                  |    |

|   | 6.3.5.1 Default State                                                    |    |

|   | 6.3.5.2 Loss of Synchronization state                                    | 98 |

|   | 6.3.5.3 Word Synchronization Acquired states                             | 98 |

|   | 6.3.5.3.1 Loss-of-Synchronization procedure                              | 08 |

|   |                                                                          | 30 |

|   | 6.3.5.3.2 No Invalid Transmission Word Detected state                                |             |

|---|--------------------------------------------------------------------------------------|-------------|

|   | 6.3.5.3.3 First Invalid Transmission Word Detected state                             |             |

|   | 6.3.5.3.4 Second Invalid Transmission Word Detected state                            | 99          |

|   | 6.3.5.3.5 Third Invalid Transmission Word Detection state                            | 99          |

|   | 6.3.5.4 Reset state                                                                  |             |

|   | 6.4 64B/66B Transmission Word Synchronization                                        | 100         |

|   | 6.4.1 Overview                                                                       |             |

|   | 6.4.2 64B/66B Transmission Word Synchronization for speed negotiation                |             |

|   | 6.4.3 Detection of an invalid 64B/66B Transmission Word                              |             |

|   | 6.5 Transmitter Training Signal Transmission Word Synchronization                    | 101         |

|   | 6.5.1 Introduction                                                                   |             |

|   | 6.5.2 Transmitter Training Transmission Word Synchronization for speed negotiation - |             |

|   | 6.6 256B/257B Transmission Word Synchronization                                      | 102         |

|   |                                                                                      |             |

|   | 6.6.2 RS-FEC rapid code Word Synchronization process                                 |             |

| 7 | FC_Port state machine                                                                | 104         |

|   | 7.1 Scope                                                                            |             |

|   | 7.2 Introduction                                                                     |             |

|   | 7.3 Normal operation states                                                          | 105         |

|   | 7.4 Active State (AC)                                                                |             |

|   | 7.5 Link Recovery                                                                    | 108         |

|   | 7.5.1 Link Recovery hierarchy                                                        | 108         |

|   | 7.5.2 LR Transmit State (LR1)                                                        | 108         |

|   | 7.5.3 LR Receive State (LR2)                                                         | 108         |

|   | 7.5.4 LRR Receive State (LR3)                                                        | 108         |

|   | 7.6 Link Failure                                                                     |             |

|   | 7.6.1 NOS Receive State (LF1)           7.6.2 NOS Transmit State (LF2)               | 109         |

|   | 7.6.2 NOS Transmit State (LF2)                                                       | 109         |

|   | 7.7.1 General                                                                        |             |

|   | 7.7.2 OLS Transmit State (OL1)                                                       |             |

|   | 7.7.3 OLS Receive State (OL2)                                                        | 1109        |

|   | 7.7.4 Wait for OLS State (OL3)                                                       | 110         |

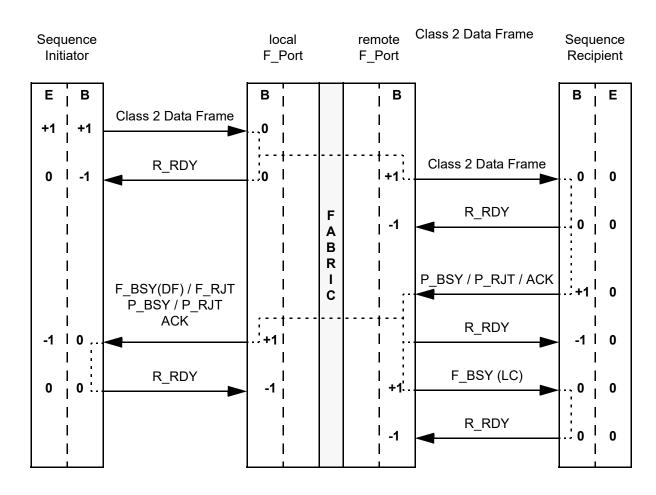

|   | 7.8 Primitive Sequence Protocols                                                     | 110         |

|   | 7.8.1 Functions                                                                      | 110         |

|   | 7.8.2 Link Initialization Protocol                                                   |             |

|   | 7.8.3 Link Reset Protocol                                                            |             |

|   | 7.8.4 Link Failure Protocol                                                          | 111         |

|   | 7.8.5 Online-to-offline Protocol                                                     | 111         |

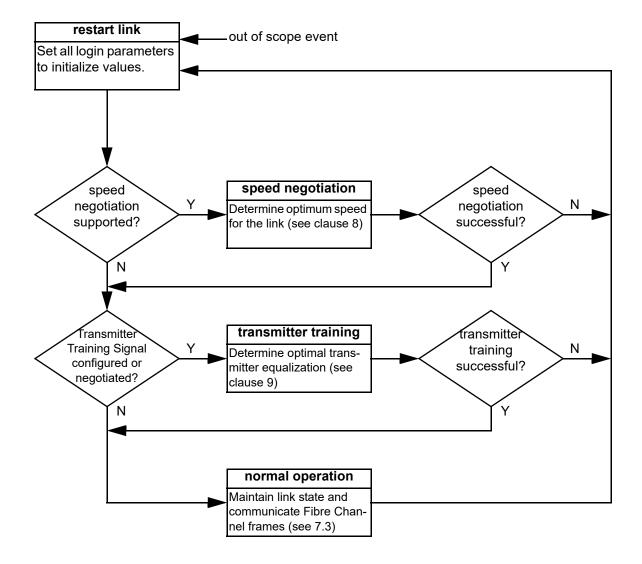

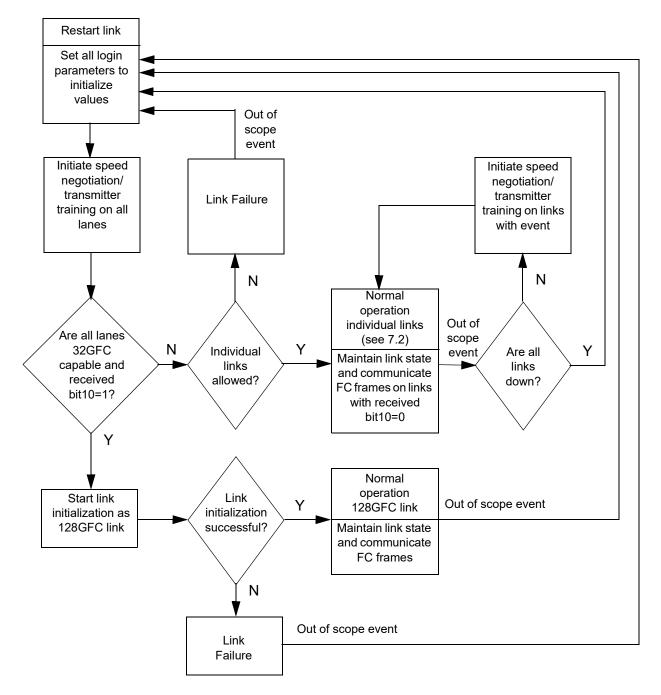

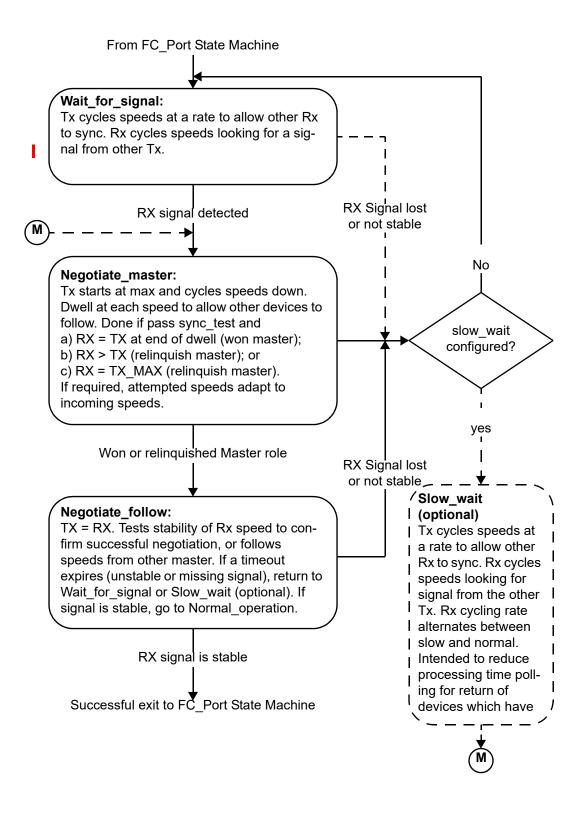

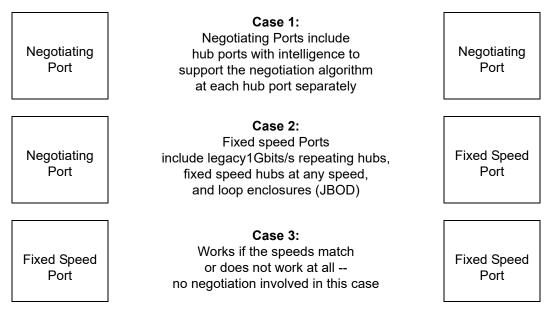

| 0 | Link speed negotiation                                                               | 110         |

| 0 | 8.1 Scope                                                                            | 112         |

|   | 8.2 Speed negotiation overview                                                       |             |

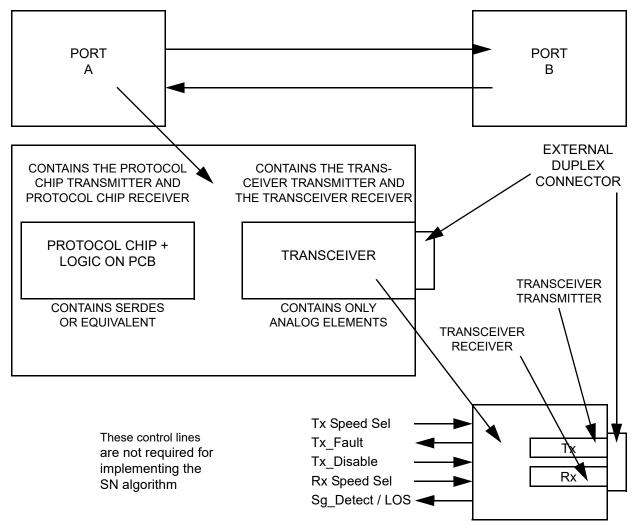

|   | 8.3 Link physical architecture and requirements                                      | 112         |

|   | 8.4 Speed negotiation requirements on L_Ports                                        | 11 <u>2</u> |

|   | 8.5 Primitives                                                                       | 114         |

|   | 8.5.1 Overview                                                                       |             |

|   | 8.5.2 32GFC speed negotiation                                                        |             |

|   | 8.5.3 128GFC speed negotiation                                                       | 115         |

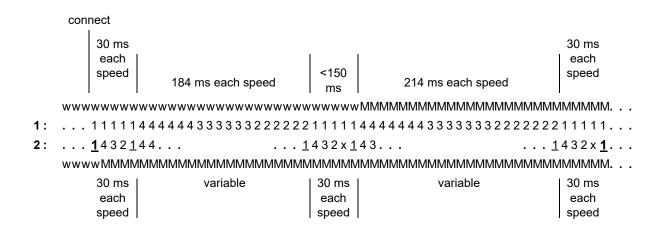

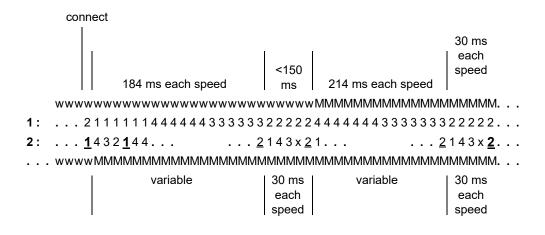

|   | 8.6 Speed negotiation algorithm                                                      | 116         |

|   | 8.6.1 Algorithm overview                                                             | 116         |

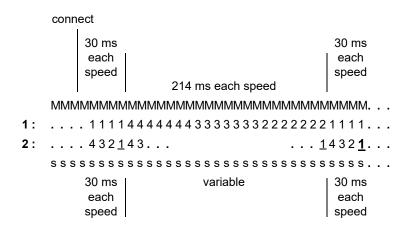

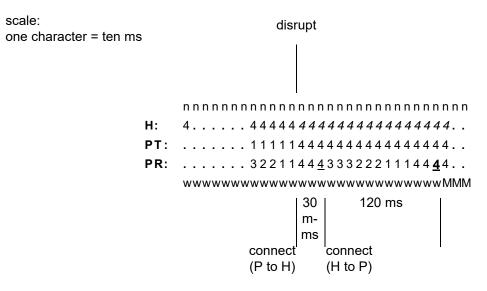

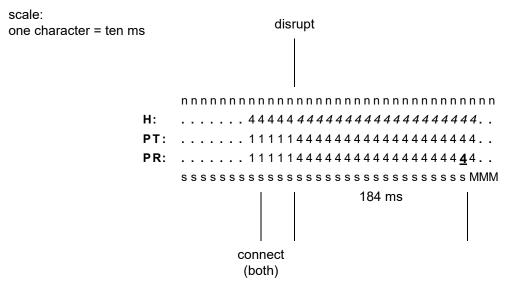

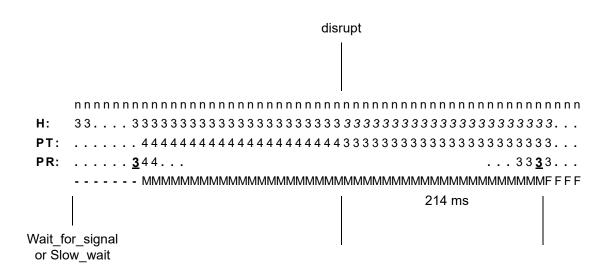

|   | 8.6.2 Speed Negotiation stage specification conventions                              | 118         |

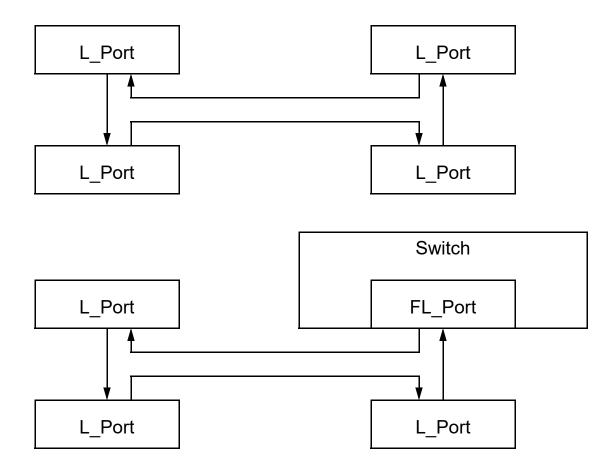

|   | 8.6.2.1 Diagramming conventions                                                      | 118         |

|   | 8.6.2.2 Terminology                                                                  | 120         |

|   |                                                                                      |             |

|    | 8.6.3 Stage 1 - Wait_for_signal                      |     |

|----|------------------------------------------------------|-----|

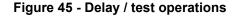

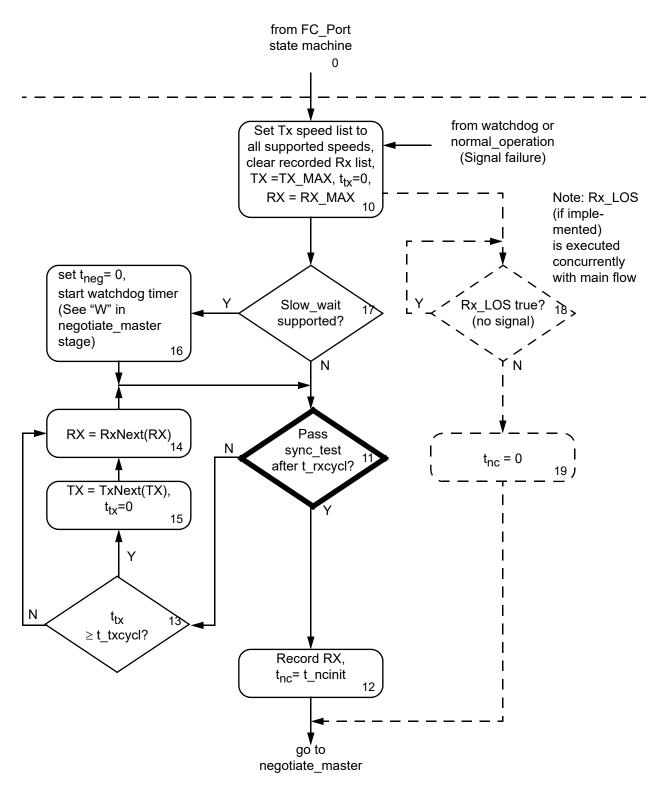

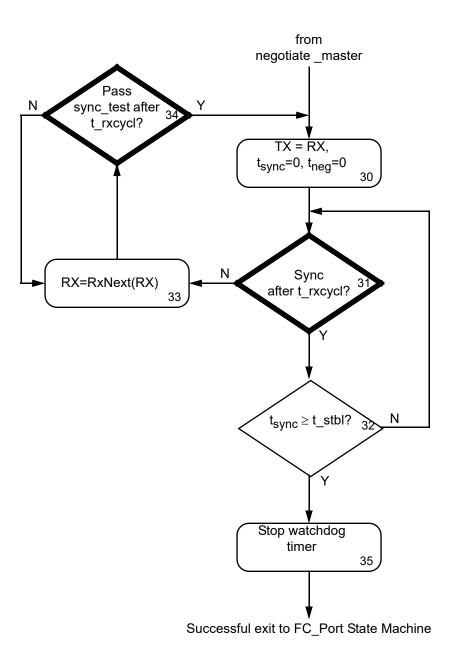

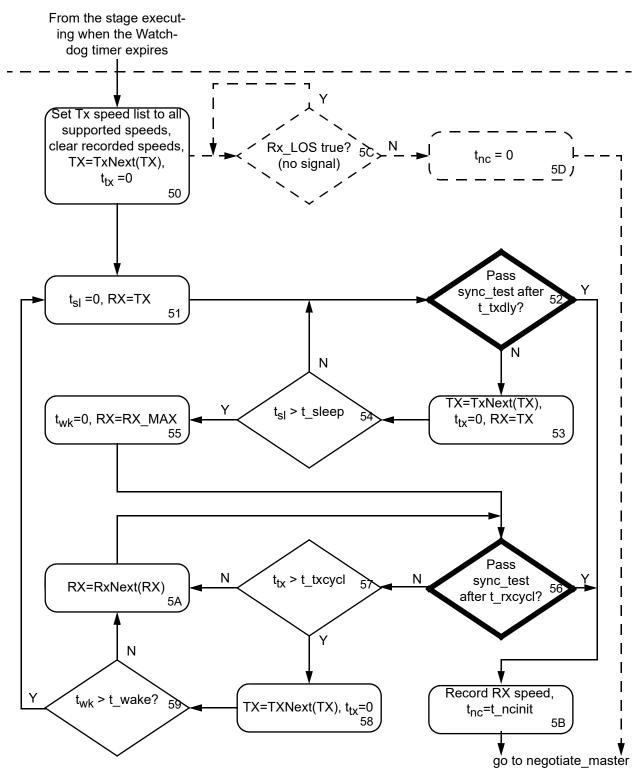

|    | 8.6.4 Stage 2 - Negotiate_master and Watchdog timer  | 123 |

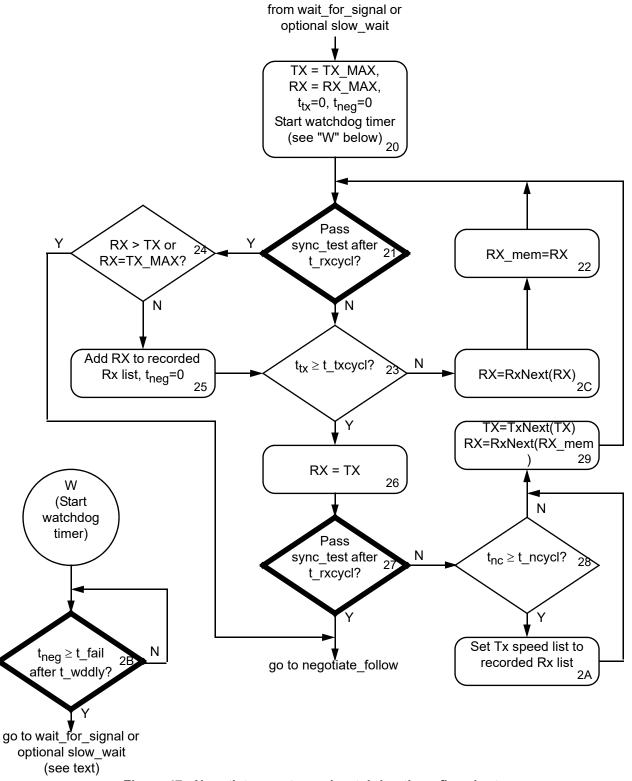

|    | 8.6.5 Stage 3 - Negotiate_follow                     | 126 |

|    | 8.6.6 Optional Stage 5 - Slow_wait                   | 127 |

|    | 8.6.7 Timing requirements                            | 129 |

| ٩  | Transmitter training                                 | 132 |

| 5  | 9.1 Scope                                            | 132 |

|    | 9.2 Overview                                         |     |

|    | 9.3 Transmitter training state machines              |     |

|    | 9.3.1 Overview                                       | 133 |

|    | 9.3.2 Timers                                         |     |

|    | 9.3.3 Variables                                      |     |

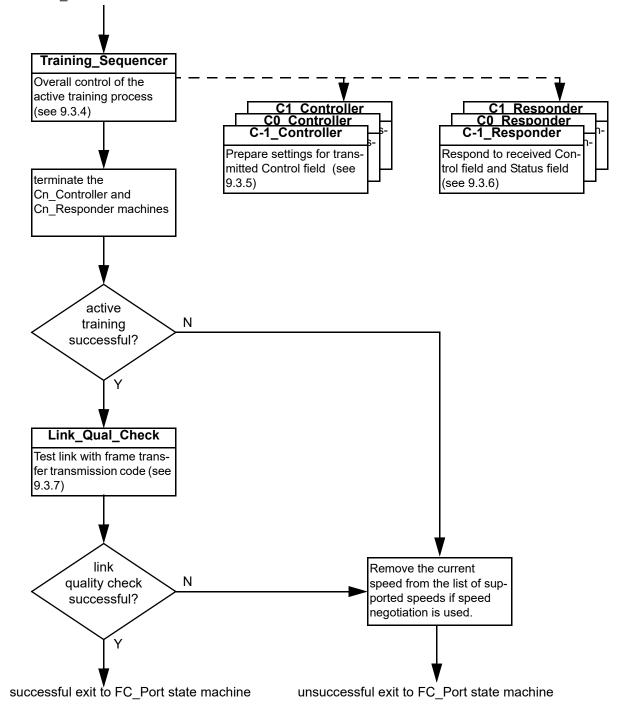

|    | 9.3.4 Training_Sequencer state machine               |     |

|    | 9.3.4.1 Overview                                     |     |

|    | 9.3.4.2 States                                       |     |

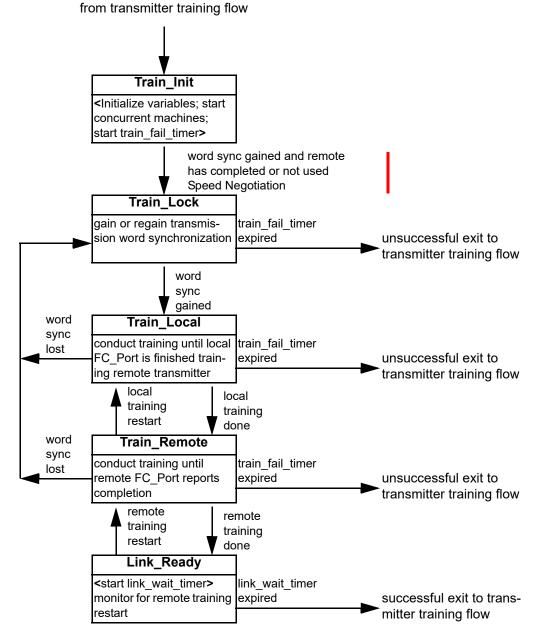

|    | 9.3.4.2.1 Train_Init                                 |     |

|    | 9.3.4.2.2 Train Lock                                 | 139 |

|    | 9.3.4.2.3 Train Local                                |     |

|    | 9.3.4.2.4 Train Remote                               |     |

|    | 9.3.4.2.5 Link Ready                                 | 140 |

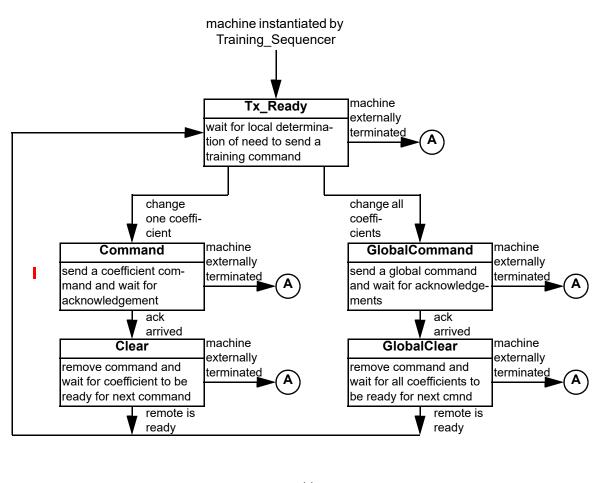

|    | 9.3.5 Cn_Controller state machines                   | 140 |

|    | 9.3.5.1 Overview                                     | 140 |

|    | 9.3.5.2 States                                       |     |

|    | 9.3.5.2.1 Tx_Ready                                   | 141 |

|    | 9.3.5.2.2 Command                                    | 142 |

|    | 9.3.5.2.3 Clear                                      | 143 |

|    | 9.3.5.2.4 GlobalCommand                              | 143 |

|    | 9.3.5.2.5 GlobalClear                                | 144 |

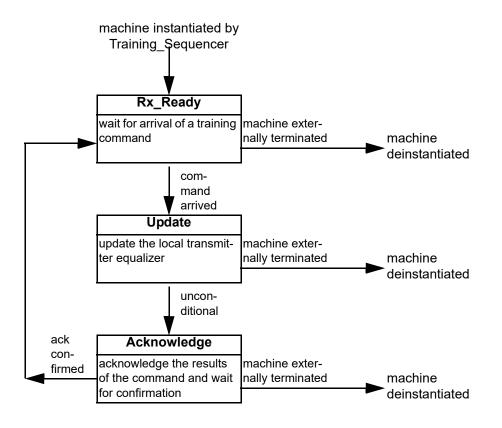

|    | 9.3.6 Cn_Responder state machines                    | 144 |

|    | 9.3.6.1 Overview                                     | 144 |

|    | 9.3.6.2 States                                       |     |

|    | 9.3.6.2.1 Rx_Ready                                   | 145 |

|    | 9.3.6.2.2 Update                                     | 146 |

|    | 9.3.6.2.3 Acknowledge                                | 147 |

|    | 9.3.7 Link_Qual_Check state machine                  | 148 |

|    | 9.3.7.1 Overview                                     |     |

|    | 9.3.7.2 States                                       |     |

|    | 9.3.7.2.1 Link_Test                                  | 148 |

| 10 | Energy Efficient Fibre Channel                       | 149 |

|    | 10.1 Overview                                        | 149 |

|    | 10.2 Energy Efficient Negotiation                    |     |

|    | 10.3 Energy Efficient Fibre Channel and FEC          | 149 |

|    | 10.4 Alert Signal                                    | 150 |

|    | 10.5 Transmitter Turn Off                            |     |

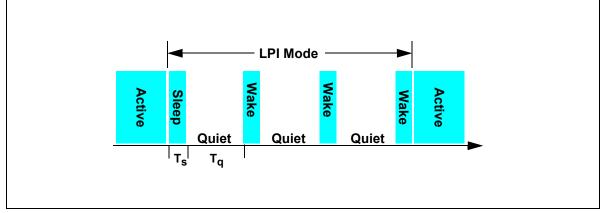

|    | 10.6 LPI Mode                                        |     |

|    | 10.6.1 Overview                                      |     |

|    | 10.6.2 LPI Mode Entry                                |     |

|    | 10.6.3 LPI Mode Timing Parameters                    |     |

|    | 10.6.4 Energy Efficient Fibre Channel State Diagrams | 152 |

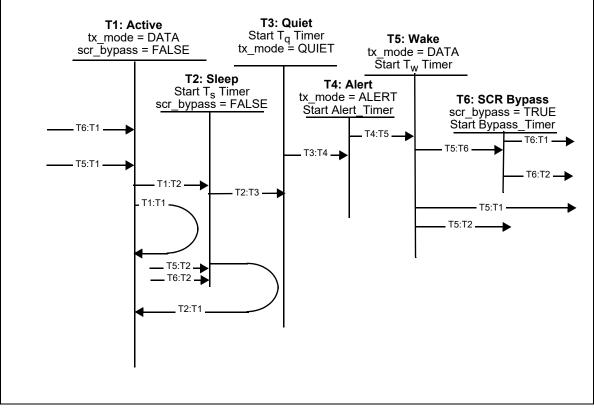

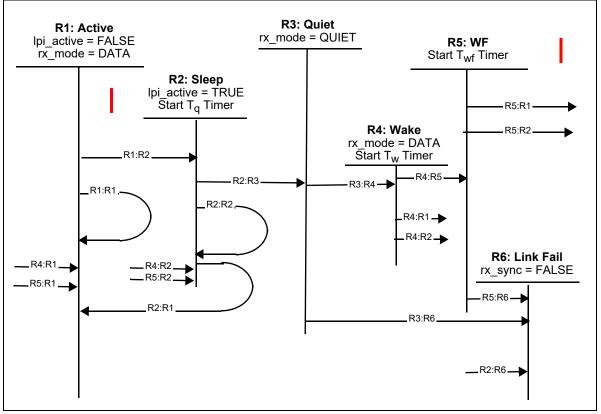

|    | 10.6.4.1 Energy Efficient State Variables            | 152 |

|    | 10.6.4.2 LPI Mode Transmitter State Diagram          | 153 |

|    | 10.6.4.3 LPI Mode Receiver State Diagram             | 154 |

| 11 | Frame Transmission and Reception              | 157 |

|----|-----------------------------------------------|-----|

|    | 11.1 Scope                                    | 157 |

|    | 11.2 General frame format                     | 157 |

|    | 11.3 Frame transmission and reception         | 157 |

|    | 11.3.1 Overview                               |     |

|    | 11.3.2 Fill Words                             |     |

|    | 11.3.3 Frame Transmission                     |     |

|    | 11.3.4 Frame byte order                       | 158 |

|    | 11.3.5 Emission Lowering Protocol             | 160 |

|    | 11.3.6 Frame Scrambling                       | 160 |

|    | 11.3.7 Start-of-Frame (SOF) delimiter         | 161 |

|    | 11.3.7.1 Introduction                         | 161 |

|    | 11.3.7.2 SOF Initiate (SOFix)                 | 161 |

|    | 11.3.7.2.1 Applicability                      | 161 |

|    | 11.3.7.2.2 SOF Initiate Class 2 (SOFi2)       | 161 |

|    | 11.3.7.2.3 SOF Initiate Class 3 (SOFi3)       | 161 |

|    | 11.3.7.3 SOF Normal (SOFnx)                   | 101 |

|    | 11.3.7.3.1 Applicability                      | 101 |

|    | 11.3.7.3.2 SOF Normal Class 2 (SOFn2)         | 162 |

|    | 11.3.7.4 SOF Fabric (SOFf)                    | 162 |

|    | 11.3.8 End-of-Frame (EOF) delimiter           | 162 |

|    | 11.3.8.1 Introduction                         | 162 |

|    | 11.3.8.2 Valid frame content                  |     |

|    | 11.3.8.2.1 EOF Normal (EOFn)                  |     |

|    | 11.3.8.2.2 EOF Terminate (EOFt)               | 163 |

|    | 11.3.8.3 Invalid frame content                | 163 |

|    | 11.3.8.3.1 General                            |     |

|    | 11.3.8.3.2 End of Frame Abort (EOFa)          |     |

|    | 11.3.8.3.3 EOF Invalid (EOFni)                | 163 |

|    | 11.3.9 Frame reception                        | 164 |

|    | 11.3.9.1 Rules                                | 164 |

|    | 11.3.9.2 Frame validity                       | 164 |

|    | 11.3.9.3 Invalid frame processing             | 164 |

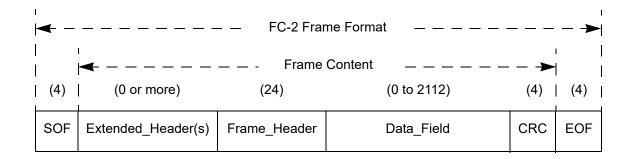

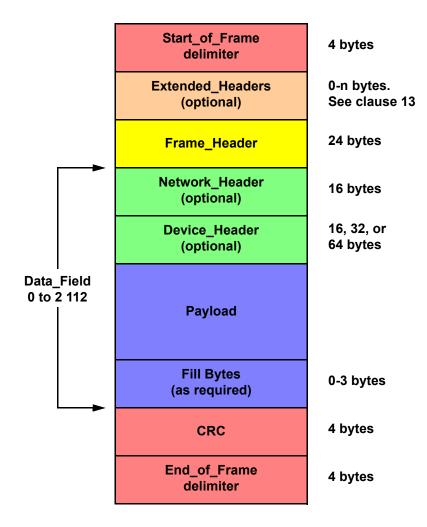

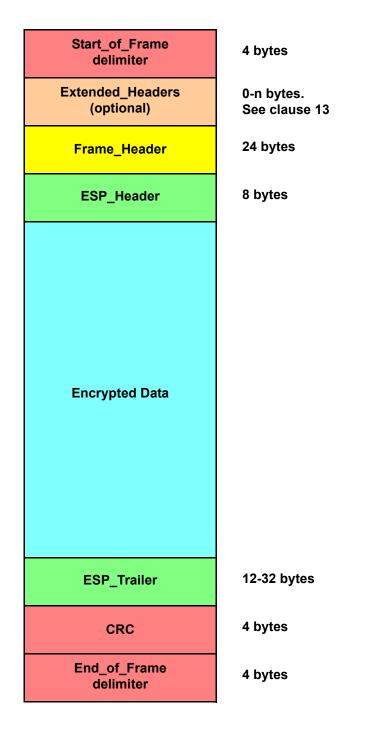

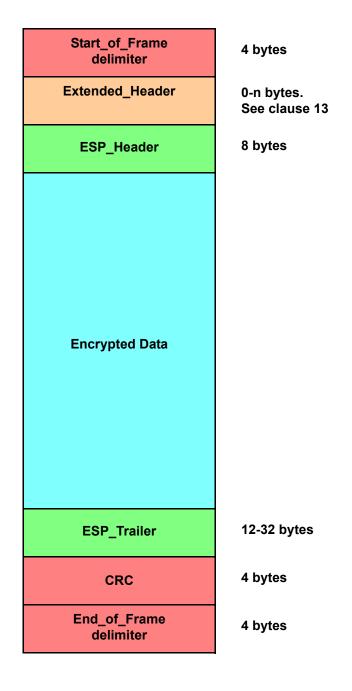

|    | 11.4 Frame Content                            | 165 |

|    | 11.4.1 Scope                                  |     |

|    | 11.4.2 Extended_Headers                       | 165 |

|    | 11.4.3 Frame_Header                           |     |

|    | 11.4.4 Data_Field                             |     |

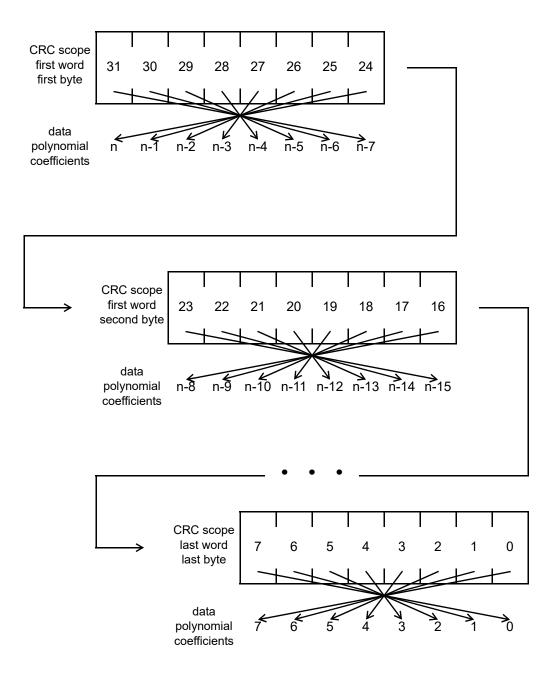

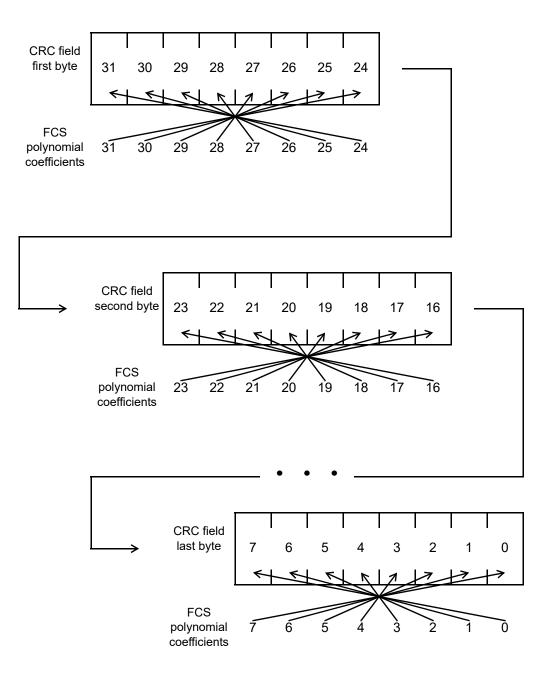

|    | 11.4.5 CRC                                    | 165 |

| 12 | Frame_Header                                  | 169 |

| 12 | 12.1 Scope                                    | 160 |

|    | 12.2 Introduction                             | 169 |

|    | 12.3 Routing Control (R_CTL)                  | 169 |

|    | 12.3.1 Introduction                           | 169 |

|    | 12.3.2 ROUTING Field                          |     |

|    | 12.3.3 INFORMATION Field                      |     |

|    | 12.4 Address identifiers (D_ID, S_ID)         | 172 |

|    | 12.4.1 General                                | 172 |

|    | 12.4.2 Reserved address identifiers           |     |

|    | 12.4.3 Destination_ID (D_ID)                  |     |

|    | 12.4.4 Source ID (S ID)                       | 172 |

|    | 12.5 Class Specific Control (CS_CTL)/Priority | 173 |

|    |                                               |     |

|    | 12.5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 173                                                                                                                                                                                              |  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    | 12.5.1.1 CS_CTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 173                                                                                                                                                                                              |  |

|    | 12.5.2 Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 174                                                                                                                                                                                              |  |

|    | 12.6 Data structure type (TYPE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 174                                                                                                                                                                                              |  |

|    | 12.7 Frame Control (F_CTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 177                                                                                                                                                                                              |  |

|    | 12.7.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 177                                                                                                                                                                                              |  |

|    | 12.7.2 Exchange Context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                  |  |

|    | 12.7.3 Sequence Context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                  |  |

|    | 12.7.4 First Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 179                                                                                                                                                                                              |  |

|    | 12.7.5 Last Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 180                                                                                                                                                                                              |  |

|    | 12.7.6 End_Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100                                                                                                                                                                                              |  |

|    | 12.7.7 CS_CTL/Priority Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 180                                                                                                                                                                                              |  |

|    | 12.7.8 Sequence Initiative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100                                                                                                                                                                                              |  |

|    | 12.7.9 ACK_Form                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100                                                                                                                                                                                              |  |

|    | 12.7.9 ACK_FORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 101 1                                                                                                                                                                                            |  |

|    | 12.7.10 Abort Sequence Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 101                                                                                                                                                                                              |  |

|    | 12.7.11 Relative offset present                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102                                                                                                                                                                                              |  |

|    | 12.7.12 Exchange reassembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 182                                                                                                                                                                                              |  |

|    | 12.7.13 FIII Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 182                                                                                                                                                                                              |  |

|    | 12.7.14 F_CTL bits on Data frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 183                                                                                                                                                                                              |  |

|    | 12.7.15 F_CTL bits on Link_Control frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 183                                                                                                                                                                                              |  |

|    | 12.8 Sequence_ID (SEQ_ID)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 184                                                                                                                                                                                              |  |

|    | 12.9 Data Field Control (DF_CTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 185                                                                                                                                                                                              |  |

|    | 12.10 Sequence count (SEQ_CNT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 186                                                                                                                                                                                              |  |

|    | 12.11 Originator Exchange_ID (OX_ID)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 186                                                                                                                                                                                              |  |

|    | 12.12 Responder Exchange_ID (RX_ID)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 187                                                                                                                                                                                              |  |

|    | 12.13 Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 187                                                                                                                                                                                              |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                  |  |

| 12 | Extended Headers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100                                                                                                                                                                                              |  |

| 13 | Extended_Headers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>188</b>                                                                                                                                                                                       |  |

| 13 | 13.1 Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 188                                                                                                                                                                                              |  |

| 13 | 13.1 Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 188<br>188                                                                                                                                                                                       |  |

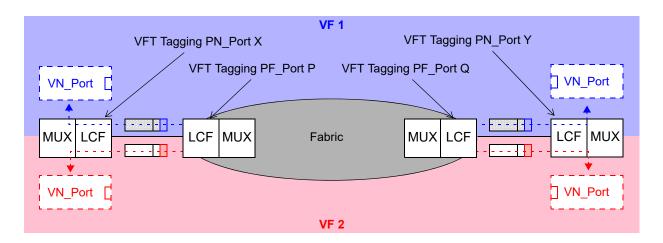

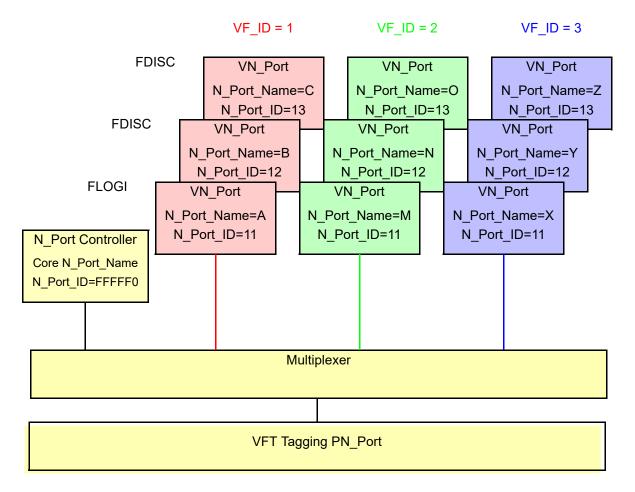

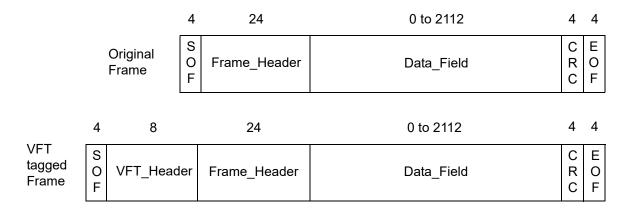

| 13 | 13.1 Scope         13.2 Introduction         13.3 VFT_Header and Virtual Fabrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 188<br>188<br>189                                                                                                                                                                                |  |

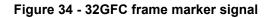

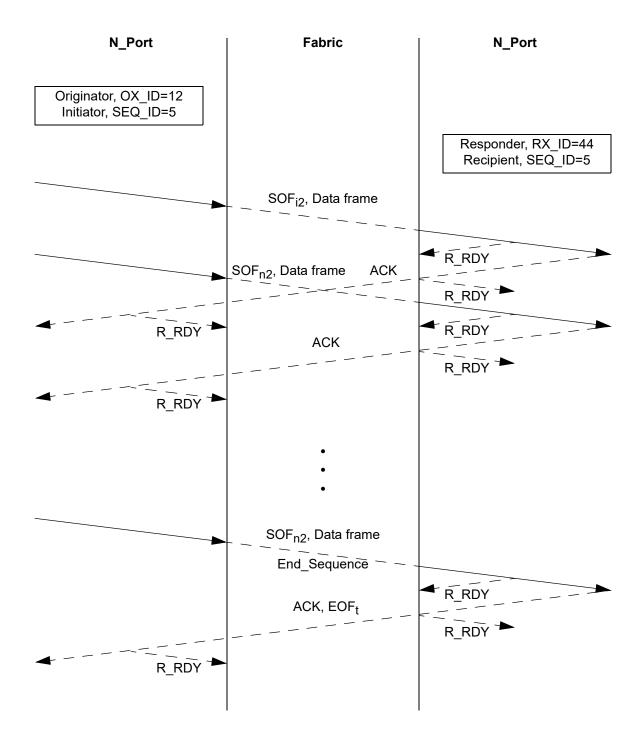

| 13 | 13.1 Scope         13.2 Introduction         13.3 VFT_Header and Virtual Fabrics         13.3.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 188<br>188<br>189<br>189                                                                                                                                                                         |  |